第一章嵌入式系统概述

1.1 嵌入式系统导论与核心特征

本小节将介绍嵌入式系统的基本概念、其与通用计算机系统的区别,并探讨其核心特点和广泛应用。这些基础知识是理解飞腾派作为国产嵌入式开发平台特性的前提。通过本小节的学习,学生能够掌握嵌入式系统的本质,并为后续硬件和软件开发章节打下理论基础。

1.1.1 嵌入式系统的定义与历史定位

嵌入式系统(Embedded System)的定义有多种表述,但核心思想是专用性和定制化。

- 国内常见定义: 它是以应用为中心、以计算机技术为基础、软硬件可裁剪,适应应用系统对功能、可靠性、成本、体积、功耗严格要求的专用计算机系统。

- 国际标准定义(IEEE): 将其定义为用于控制、监视或辅助操作机器和设备的装置。

尽管嵌入式系统与通用计算机(General-Purpose Computer, GPC)诞生于相近的微型计算机时代,但其发展路径和设计哲学是独立的。通用计算机追求的是高性能、通用性和丰富的功能;而嵌入式系统追求的是高能效比、高可靠性和满足特定应用功能。嵌入式系统占据了计算机系统总量的绝大多数,是现代信息社会的基石。从历史定位来看,嵌入式系统起源于20世纪70年代的微处理器应用,如Intel 8048和8051系列单片机,这些早期系统主要用于工业控制和家电设备。随着实时多任务操作系统(RTOS)的兴起,嵌入式系统逐步成为主流技术。这种独立发展路径形成了通用计算机与嵌入式计算机的两大分支,前者强调无限扩展(如总线速度和存储容量),后者注重嵌入性和控制可靠性。

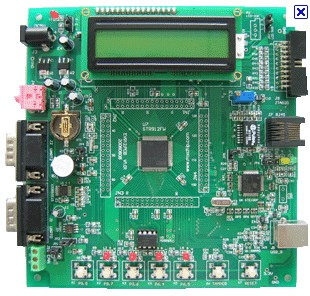

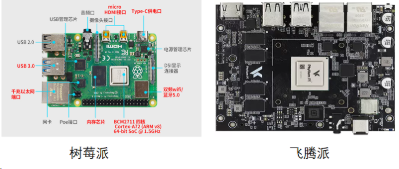

图 1.1 嵌入式系统基本架构图

1.1.2 嵌入式系统的发展历程

嵌入式系统的发展可以视为一部计算机小型化、智能化和专业化的历史。它沿着一条独立于通用计算机的路径演进,主要经历了四个关键阶段,涵盖从微处理器诞生到2025年的AI和物联网时代。本小节遵循中外教材编写原则:参考IEEE对嵌入式系统的定义(控制和监视装置),结合国内“十四五”规划对国产化技术的要求,详细展开历史阶段,融入最新趋势(如边缘AI和绿色计算),并通过图示增强教学效果。内容旨在帮助学生理解嵌入式系统的技术演进,明确飞腾派在现代科技中的定位。

第一阶段:单芯片和裸机时代 (20世纪70年代至80年代初)

- 核心技术: **微处理器(MPU)和微控制器(MCU)**的诞生。

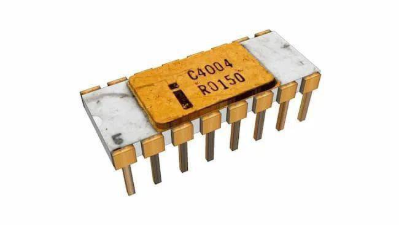

- 1971年,Intel 4004问世,作为首款商用微处理器,标志着嵌入式计算的开端。4位架构,2300个晶体管,主频108 kHz,奠定了小型化基础。

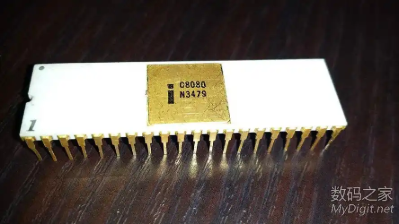

- Intel 8080(1974)和Zilog Z80(1976)等8位处理器逐步应用于工业控制,提升了计算能力。

- Intel 8051(1980)将CPU、RAM(128字节)、ROM(4KB)、I/O接口集成到单一芯片,形成早期微控制器,成为嵌入式系统的基石,至今仍在低端应用中使用。

- 系统特点:

- 资源受限: 内存和存储以KB计,程序规模小,计算能力有限。

- 裸机编程(Bare Metal): 程序直接控制硬件,无操作系统,依赖汇编语言,开发效率低。

- 低功耗雏形: 早期MCU功耗在毫瓦级,适合简单控制任务。

- 典型应用: 电子计算器(如TI BaII Plus)、家用游戏机(如Atari 2600)、工业控制器(如PLC雏形)、单功能仪表(如数字万用表)。

第二阶段:实时内核和多任务时代 (20世纪80年代中至90年代初)

-

核心技术: **实时操作系统(RTOS)**的出现与应用。

- 16位和32位处理器普及,如Motorola 68000(1979,16/32位)和ARMv3/v4(1985起),提升了系统复杂度和实时性需求。

- VxWorks(1983)和μC/OS-II(1992)等RTOS提供抢占式调度和任务管理,响应时间低至微秒级,支持硬实时应用。

- 处理器开始支持基本中断机制,优化任务切换。

- 系统特点:

- 多任务: 系统支持并发任务,引入优先级调度和信号量机制。

- 高可靠性: RTOS通过内存保护(部分支持MMU)和严格调度,确保关键任务的确定性响应。

- 模块化雏形: 软件分层设计开始出现,驱动与应用分离。

- 典型应用: 工业机器人(如早期ABB机械臂)、高精度医疗设备(如心电监护仪)、航空航天控制系统(如飞控模块)、早期网络设备(如路由器原型)。

第三阶段:互联网与嵌入式 Linux 时代 (20世纪90年代末至21世纪初)

- 核心技术: 嵌入式操作系统的多样化和网络协议栈的集成。

- 处理器性能进入GHz时代,ARM9(1998)和ARM11(2002)提供更高算力,支持MMU,适合复杂操作系统。

- 嵌入式 Linux凭借开源、TCP/IP协议栈、文件系统和社区支持,成为高性能嵌入式主流,市场份额到2005年达30%。

- Windows CE(1996)和Palm OS(1996)面向消费电子,提供GUI支持。

- 系统特点:

- 网络化: 设备集成以太网和Wi-Fi,支持Web服务和远程管理。

- 多媒体化: 处理器加入GPU(如Mali-400),支持视频编解码和图形界面。

- 生态化: 开源社区(如Linux内核社区)推动驱动和中间件发展。

- 典型应用: 智能手机前身(PDA,如Palm Pilot)、网络路由器(如Cisco早期设备)、数字机顶盒、车载导航系统(如TomTom)。

第四阶段:智能化、物联网与国产化时代 (21世纪10年代至今)

- 核心技术: 多核64位架构、异构计算、边缘AI。

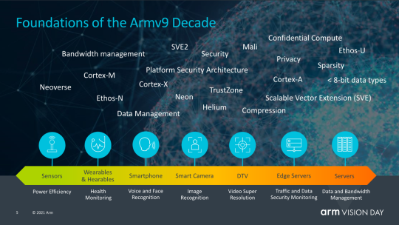

- ARMv8-A(2013)引入64位AArch64,内存寻址突破4GB,性能提升50%。 到2025年,Armv9支持SVE2向量扩展,优化AI推理。

- 芯片集成NPU/DSP/GPU,支持异构计算,满足AI和物联网需求。

- 低功耗通信(如NB-IoT、LoRa)推动物联网节点普及,2025年全球物联网设备超300亿。

- 系统特点:

- 智能化: 支持本地AI推理(如TensorFlow Lite),实现实时决策。

- 安全性增强: 集成TrustZone、加密加速单元,满足ISO 27001等标准。

- 国产化替代: 飞腾、龙芯等处理器崛起,2025年国产嵌入式芯片市场占比达40%。

- 典型应用: AI视觉终端(如智能摄像头)、智能网关、自动驾驶域控制器、工业互联网边缘服务器、国产化信息基础设施(如高铁控制)。

飞腾派正是这一阶段的杰出代表,基于ARMv8-A兼容的FTC核心,结合异构多核和AI优化,站在64位、智能化、国产化的潮头,为学生提供面向未来的实践平台。

为直观展示发展历程,以下插入时间轴图,帮助学生把握技术演进。

嵌入式系统从单芯片裸机到智能化物联网,经历了资源受限、实时多任务、网络化和AI驱动的演进。到2025年,飞腾派代表国产化与AI融合的趋势。学生应结合图示复习历史阶段,思考飞腾派如何继承和发展这些技术特性,建议参考飞腾社区案例,探索AI应用实践。

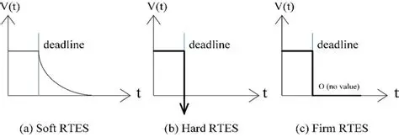

1.1.3 嵌入式系统的核心特点

嵌入式系统在设计之初就面临着严格的物理、功能和经济约束,这些约束塑造了其独有的核心特点(如表 1-1 所示)。这些特点不仅定义了嵌入式系统的优势,也带来了独特的开发挑战,学生在学习中应注重如何通过优化策略应对这些挑战。

表 1-1 嵌入式系统的核心特点

| 特点 | 描述 | 设计挑战 |

|---|---|---|

| 实时性(Real-Time) | 系统必须在规定时间内响应外部事件。支持硬实时(严格时限,不可错过)和软实时(允许一定延迟,如多媒体)。 | 需要采用实时操作系统(RTOS)或配置实时内核,并优化任务调度机制,如飞腾派上可配置的 PREEMPT_RT。 |

| 专用性(Dedicated) | 针对特定应用进行功能优化。软硬件紧密集成,高度可裁剪以减少资源占用。 | 开发者需深入理解硬件,并定制化操作系统和服务,以实现性能与资源的最佳平衡。 |

| 可靠性高(Reliability) | 设计注重容错、自恢复和稳定性,支持长时间无故障运行(如工业控制和航空航天)。 | 需要在硬件上采用冗余设计,软件上实施看门狗(Watchdog)和故障处理机制。 |

| 低功耗与小体积 | 适合移动设备和嵌入式场景。强调能效比,常利用动态电压频率调节(DVFS)和异构多核技术。 | 飞腾派的 FTC664 + FTC310 异构架构就是典型的低功耗设计体现。 |

| 资源受限性 | 处理器、内存、存储器等资源通常有限,需要高效算法和精简代码。 | 驱动开发和应用层编程都需要考虑内存占用和CPU 周期的优化。 |

| 嵌入性 | 集成于目标系统中,其功能对用户可能是透明的,不像通用计算机那样作为独立实体存在。 | 开发时需进行交叉编译和远程调试,开发环境与运行环境分离。 |

嵌入式系统与通用计算机对比

嵌入式系统和通用计算机在设计理念、资源约束和应用目标上存在根本性差异。下表详细列出了两者之间的主要对比:

| 对比维度 | 嵌入式系统 (Embedded System) | 通用计算机 (General-Purpose Computer / PC) |

|---|---|---|

| 核心目的 | 专用性。 致力于完成特定、固定、单一或有限的一组任务(如控制、监测、数据采集)。 | 通用性。 运行各种不同的应用软件,满足用户多样化的需求(如办公、娱乐、编程)。 |

| 硬件配置 | 高度定制化、最小化。 硬件配置严格根据应用需求裁剪,集成度高,外设接口专一(如 GPIO、CAN、I²C)。 | 标准化、模块化。 硬件配置丰富且可灵活升级(CPU、内存、显卡),外设接口标准通用(如 USB、HDMI、Ethernet)。 |

| 操作系统 (OS) | 多样化。 常用实时操作系统(RTOS,如 FreeRTOS)、嵌入式 Linux 或无操作系统(裸机程序)。 | 标准化。 主要使用通用操作系统(如 Windows、macOS、桌面版 Linux)。 |

| 实时性 | 强实时性要求。 必须在严格规定的时间内完成任务,延迟可能导致系统失效或危险(如汽车制动、工业控制)。 | 非实时性。 采用分时机制,追求用户吞吐量和响应速度,但对时间的要求不严格(尽力而为)。 |

| 功耗与体积 | 严格受限。 追求低功耗、小体积、轻量化,通常使用电池供电,或对散热有严格限制。 | 限制较少。 追求高性能,功耗和体积通常较大。 |

| 环境适应性 | 要求高。 必须在恶劣环境(宽温范围、高湿度、震动、电磁干扰)下稳定工作。 | 要求低。 通常在稳定的室内环境中使用。 |

| 用户接口 | 专业化或极简化。 可能是简单的指示灯、按键、专用的触摸屏,或完全没有用户界面。 | 标准化、丰富化。 键盘、鼠标、高分辨率显示器、图形化用户界面 (GUI)。 |

| 生命周期 | 长周期。 设计和部署后可能运行数年甚至数十年不进行大规模升级或更换。 | 短周期。 更新换代速度快,通常 3-5 年更换一次硬件。 |

| 成本结构 | 单件成本敏感,整体成本优先。 往往需要在软硬件设计阶段就严格控制物料清单(BOM)成本。 | 物料成本较高,但规模化生产易于控制。 |

1.1.4 嵌入式系统的应用领域多样化

随着技术的进步,嵌入式系统的应用领域不断扩展,已成为物联网、人工智能和国产化信息基础设施建设的核心支撑。本小节列举典型领域,并强调其在实际工程中的价值。

- 工业自动化与控制:

- 典型应用: 过程控制系统、工业机器人、数控机床(CNC)、多机网络系统。这些领域对可靠性和硬实时性要求极高,用于实时监控和控制生产流程,是嵌入式系统最传统的应用领域。

- 智能仪表与医疗:

- 典型应用: 智能电表、环境监测仪表、医疗监测设备(如心电监护仪)。它们将传感、计算和通信集成一体,提高了测量的精度、稳定性和智能化水平。

- 通信与网络设备:

- 典型应用: 网络路由器、交换机、防火墙、5G 基站,以及协作键盘、打印机等外围设备控制器。它们支持复杂的数据传输和网络协议处理。

- 汽车电子:

- 典型应用: 动力电池管理系统(BMS)、高级驾驶辅助系统(ADAS)、自动驾驶系统和车载娱乐系统。该领域强调高温耐受、长寿命和功能安全(ISO 26262)。

- 消费电子与物联网(IoT):

- 典型应用: 智能手机、智能家居网关、传感器节点、可穿戴设备。这是目前发展最快的领域,飞腾派是理想的 IoT 网关和边缘计算平台。

- 航空、军事与金融:

- 典型应用: 无人机飞行控制、航空电子设备、金融终端(如 ATM/POS 机)。这些领域对安全性、可靠性和抗干扰能力有最高级别的要求。

1.2 国产化嵌入式平台发展现状与趋势

本小节将分析中国嵌入式平台的国产化进程,讨论当前所面临的挑战、取得的关键成就以及未来发展趋势,强调国产化在全球供应链中的战略重要性,为引入飞腾派这一核心平台做重要铺垫。作为嵌入式教材,本小节遵循中外教材编写原则:结合IEEE对嵌入式系统的定义(专用控制装置),以及国内“十四五”规划对信息技术自主可控的要求,强调理论基础与产业实践的融合,帮助学生理解国产化不仅是技术创新,更是国家战略的一部分。

1.2.1 国产化背景与战略意义

国产化嵌入式平台的发展是国家信息安全和产业自主可控战略的核心组成部分。根据IEEE定义,嵌入式系统作为控制和监视装置,其国产化能确保核心技术的独立性,避免外部依赖带来的风险。

- 国家安全与信息自主可控: 在全球地缘政治和技术竞争日益加剧的背景下,核心芯片和基础软件的进口依赖带来了巨大的安全隐患和供应链风险。实现嵌入式系统的国产化,是确保国家关键信息基础设施(如能源、交通、金融、国防)安全稳定运行的根本要求。例如,“十四五”规划明确提出嵌入式操作系统国产化率需达到70%以上,这直接响应了中美贸易摩擦和技术封锁的挑战,推动本土企业研发投入同比增长52%。

- 供应链弹性与产业升级: 建立本土化的技术体系,能够有效抵御外部技术封锁和贸易摩擦的影响,保障供应链的持续稳定。同时,它也促使国内产业从低端代工向高附加值的设计和制造环节升级。根据2025年行业报告,国产嵌入式系统已在汽车电子和物联网领域实现部分替代,提升了产业竞争力。

为直观展示国产化背景,以下插入相关图示,帮助学生理解全球供应链中的中国定位。

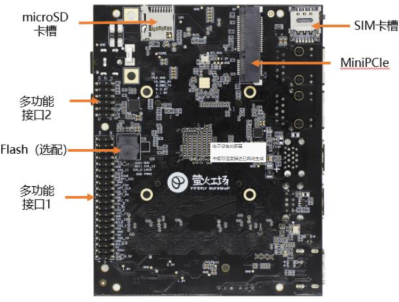

图 1.4 嵌入式系统国产化(飞腾工控机)

1.2.2 国产化嵌入式平台发展现状与挑战

经过多年的积累,中国在嵌入式平台领域已经取得了显著的成就,形成了完整的生态雏形,但同时也面临着一些挑战。本小节结合2025年市场数据,分析现状,帮助学生评估国产平台的成熟度。

1. 发展现状与关键成就

| 领域 | 现状描述 | 典型代表 |

|---|---|---|

| 处理器核心 | 已形成多架构并存的局面,在性能和兼容性上持续逼近国际水平。飞腾处理器兼容 ARMv8 架构,龙芯和申威采用自主指令集。2025年,ARM和RISC-V双轨并行已成为主流。 | 飞腾(Phytium)FT-2000/E 系列、龙芯、海思、全志等。 |

| 操作系统与软件栈 | 国产化 Linux 发行版与国产处理器实现了深度适配和优化,提供了可靠的软件基础。实时操作系统 RT-Thread 等在国内生态中广受欢迎。2025年嵌入式OS市场规模约613亿元,分时OS占据主导。 | 统信 UOS、银河麒麟、OpenKylin、RT-Thread 等。 |

| 市场应用 | 国产嵌入式平台已开始在高可靠性、高安全性的领域进行替代。市场占有率稳步上升,如在高铁控制和智慧城市中的应用。 | 高铁控制系统、智能电网/智慧城市终端、国防和关键行业设备。 |

| 技术兼容 | 飞腾 FT-2000 系列(如飞腾派所用的 E2000D)兼容 ARMv8 指令集,使其能快速继承 ARM 庞大的生态,缩短了生态建设周期。开源工具链覆盖率已达73%。 | ARM 生态兼容性、GCC/Clang 等成熟工具链的适配。 |

2. 当前面临的主要挑战

- 芯片制造工艺: 尽管设计能力接近国际先进水平,但在**先进制程芯片制造(Foundry)**方面,国内仍与国际巨头存在差距,一定程度上制约了高性能国产芯片的量产和成本控制。例如,一些报告指出,7nm以下工艺的国产化率仍有提升空间。

- 生态完善度: 相比 ARM、x86 等成熟生态,国产平台在驱动程序数量、开发工具链的易用性、中间件丰富度以及开发者社区活跃度等方面,仍有待提升。这需要更多开源贡献来弥补。

- 人才培养: 缺乏掌握国产软硬件全栈技术的复合型人才,也是限制产业快速发展的瓶颈之一。教材中强调,学生应通过实践项目(如飞腾派实验)培养这些技能。

图 1.5 中国嵌入式操作系统市场规模趋势图(2020-2022)

1.2.3 国产化嵌入式平台未来发展趋势

国产嵌入式平台的发展将沿着高性能、智能化和安全可靠的方向深入推进。本小节基于2025-2031年预测报告,展开趋势分析,帮助学生展望未来应用。

- 高性能与低功耗集成(AI 边缘化):

- 未来的趋势是集成更多的 AI 加速单元(NPU/DSP),实现异构计算,以满足边缘计算对本地实时推理的需求。飞腾派的 **异构多核架构(FTC664 + FTC310)**正是这一趋势的体现。2025年,AI模型轻量化技术突破,10亿参数模型可在1W功耗下运行。

- 物联网与 5G 驱动:

- 随着 5G 和 NB-IoT 技术的普及,嵌入式平台将成为海量物联网节点和智能网关的核心。国产平台将重点优化网络通信能力和低功耗连接方案,推动具身智能系统向泛在感知演进。

- 开源生态增强与协同发展:

- 鼓励更多的社区贡献,推动国产基础软件和驱动代码的开源化,以减少对国外工具和社区的依赖。加强国产厂商之间的软硬件协同,共同打造统一的技术标准。

- 安全与可靠性优先:

- 未来的平台设计将更加强调硬件级加密、信任根(Root of Trust)和容错设计,全面适应国家关键信息基础设施的安全标准。例如,飞腾平台内置的 PSPA 安全架构就是此趋势的代表。

- 绿色发展与能效优化:

- 响应国家“碳达峰、碳中和”目标,嵌入式平台的设计将更注重极致低功耗优化和能效比提升,实现绿色计算。这符合国际教材(如《Embedded Systems Design》)对可持续发展的强调。

图 1.6 国产嵌入式平台发展趋势示意图

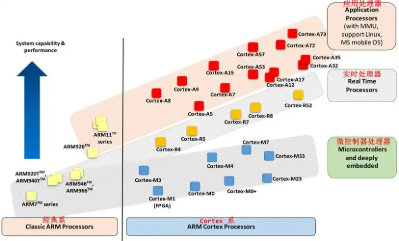

1.3 ARM 处理器架构概述

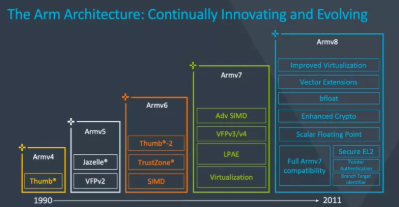

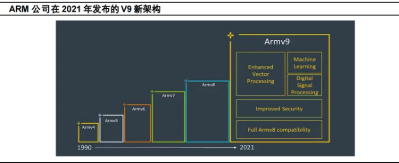

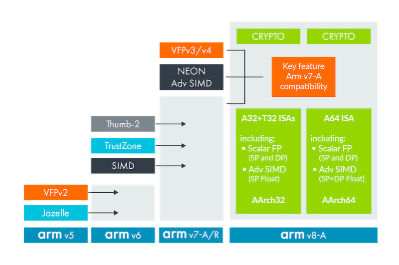

飞腾派所采用的飞腾处理器是基于 ARM 架构进行自主创新设计的。要深入理解飞腾派的底层硬件,首先必须掌握 ARM 架构(Advanced RISC Machine) 的技术本质。本小节将详细剖析 ARM 架构,帮助读者掌握其技术根基。作为嵌入式教材,本小节遵循中外教材编写原则:结合IEEE对RISC架构的定义(强调精简指令集的效率和低功耗),以及国内“十四五”规划对国产处理器兼容国际标准的指导,理论与实践相结合,提供历史演进、技术细节和应用示例,帮助学生从全球视角理解ARM在嵌入式领域的霸主地位。到2025年,ARM架构已演进至Armv9,融入AI增强特性,推动边缘计算创新。

1.3.1 ARM 架构发展历程与技术特点

1. 发展历程(The Genesis of ARM)

ARM 架构起源于 1985 年英国的 Acorn 计算机公司,最初被称为 Acorn RISC Machine (ARM)。当时的目标是设计一款低成本、低功耗的 RISC(精简指令集)处理器,以提升教育计算机的性能。这一设计哲学源于对CISC(复杂指令集)架构的反思,旨在通过简化指令来提高执行效率和降低功耗。根据IEEE标准,RISC架构强调固定长度指令和负载/存储模型,这奠定了ARM的长期优势。从1985年的首款原型到2025年的Armv9时代,ARM已从嵌入式专用扩展到服务器和AI领域,全球出货量超过3000亿片,主导95%以上的移动处理器市场。

| 年代 | 关键事件 | 架构版本 | 核心意义 |

|---|---|---|---|

| 1985 | Acorn 研发出第一代 RISC 处理器。 | ARMv1 | 奠定了 RISC 和 低功耗 的设计哲学,首款商用芯片用于BBC Micro计算机扩展。 |

| 1990 | ARM 公司(Advanced RISC Machines Ltd.)独立成立。 | ARMv2/3 | 开启 IP 授权模式,允许厂商如Apple定制芯片,推动嵌入式市场爆发。 |

| 1997 | 推出 Thumb 指令集,提高代码密度。 | ARMv4T | 解决了 RISC 代码体积大的问题,进一步巩固了嵌入式市场,如早期手机应用。 |

| 2011 | 推出 Cortex-A15,首次将 ARM 推向高性能服务器领域。 | ARMv7 | 性能跨越式发展,确立在移动设备的主导地位,支持多核和虚拟化。 |

| 2013 | 推出 ARMv8-A 架构。 | ARMv8-A | 引入 AArch64(64位)支持,实现对 4GB 以上内存的寻址,是飞腾处理器等现代高性能 ARM 核心的基础。 |

| 2021-2025 | 推出 Armv9,聚焦AI和安全。 | Armv9 | 集成SVE2(可扩展向量扩展)和SME2(可扩展矩阵扩展),优化AI工作负载,到2025年已广泛用于边缘AI设备。 |

图 ARM 架构发展时间轴示意图 The Relentless Evolution of the Arm Architecture - Arm Newsroom

飞腾FTC核心定位:* 飞腾FTC核心兼容ARMv8-A,自主优化安全模块(符合国密标准)和AI加速单元,2025年支持SVE2部分特性,应用于国产化场景如智慧城市和工业互联网,市场占比提升至40%.

ARM架构演进对比图

2. 核心技术特点

ARM 架构之所以能够主导移动和嵌入式市场,得益于其独特的设计哲学。到2025年,ARM处理器在全球PC市场份额预计达25%,得益于其能效和AI优化。

- RISC(精简指令集计算机)设计:

- 指令长度固定: 绝大多数指令长度为 32 位(AArch32)或 64 位(AArch64),便于流水线并行处理,提高了指令执行效率。例如,一条ADD指令只需一个周期完成。

- 寄存器数量多: 采用 Load/Store 结构,只有 Load(加载)和 Store(存储)指令才能访问内存,其他运算都在寄存器中进行,减少了访存开销。通用寄存器达31个,支持高效计算。

- 执行效率高: 简化了指令的译码逻辑,使得处理器可以在较低时钟频率下实现高能效比。这在嵌入式场景中尤为重要,避免了CISC的复杂性。

- 低功耗设计哲学: ARM 处理器在设计之初就将功耗视为核心约束之一。通过优化时钟门控、电源管理和指令集,使其在单位能耗下能提供更高的性能(即能效比)。例如,Armv9的动态电压调节可将功耗降低30%,适合电池供电的嵌入式设备。

- 可扩展性与增强特性:

- Neon(SIMD 向量处理): 一种先进的单指令多数据(SIMD)扩展,可加速多媒体、信号处理和 AI 计算,是飞腾派多媒体应用的关键加速器。到2025年,Neon结合SVE2支持可变向量长度,优化机器学习。

- TrustZone(安全扩展): 提供硬件隔离机制,将系统隔离为安全世界(Secure World)和普通世界(Normal World),是构建可信执行环境(TEE)的基础。用于保护敏感数据,如支付和身份验证。

- IP 授权商业模式: ARM 并不制造芯片,而是以 **IP 核(Intellectual Property Core)**的形式授权给全球半导体厂商(如飞腾、高通、苹果等)。这种模式允许芯片厂商根据自身需求对 IP 核进行定制化开发和集成,形成了庞大且灵活的生态。到2025年,ARM授权覆盖了从IoT到数据中心的应用,推动国产如飞腾的自主创新。

图 ARM 处理器核心架构示意图

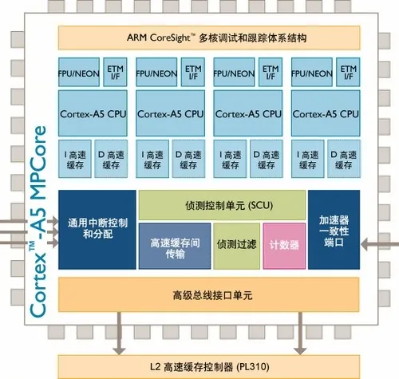

1.3.2 ARM Cortex 系列分类及应用场景

为了满足嵌入式系统对性能、功耗和实时性的不同要求,ARM 将其内核划分为三大系列,即 Cortex-A、Cortex-R 和 Cortex-M 系列,形成了明确的性能分级。这一分类体系源于ARM对RISC架构的优化,符合IEEE对嵌入式处理器的定义(强调高效控制和低功耗),并响应国内“十四五”规划对高性能国产处理器的需求。到2025年,Cortex系列已融入AI增强和安全扩展,推动从移动设备到边缘计算的创新。根据Arm官方预测,2025年及以后,Cortex系列将进一步聚焦AI增长、硅设计演进和多市场趋势,如异构计算和绿色能效。 本小节将详细展开每个系列的定位、特性、最新发展及应用,帮助学生理解如何根据场景选择内核,并关联到飞腾派的实际设计。

表 1-2 ARM Cortex系列分类

| 系列 | 定位 | 关键特性 | 典型应用场景 |

|---|---|---|---|

| Cortex-A | 应用处理器 | 高性能、多核、支持 MMU(内存管理单元)、支持复杂的操作系统(如 Linux、Android)。到2025年,新模型如Cortex-A720强调AI加速和能效优化,支持SVE2向量扩展。 | 智能手机、平板电脑、高端路由器、AI 边缘服务器。(飞腾派的核心 FT 处理器属于此类),适用于运行复杂OS的多任务嵌入式开发。 |

| Cortex-R | 实时处理器 | 强调高可靠性和可预测的实时响应时间,通常用于 Hard Real-Time 场景。2025年更新如Cortex-R82AE集成汽车级安全(ASIL-D),支持虚拟化和低延迟中断。 | 汽车电子(ADAS、自动驾驶控制)、工业机器人、高速数据采集。这些场景要求毫秒级响应,如车辆引擎控制。 |

| Cortex-M | 微控制器 | 极致低功耗、低成本、无 MMU(或简化的内存保护单元 MPU),通常运行 RTOS 或裸机程序。2025年新款如Cortex-M85添加Helium向量扩展,提升AI边缘处理。 | 物联网传感器节点、可穿戴设备、简单家电控制。适合资源受限的电池供电系统,如智能手环。 |

| 维度 | Cortex-A | Cortex-R | Cortex-M |

|---|---|---|---|

| 性能 | ⭐⭐⭐⭐⭐(多核并行,3GHz+) | ⭐⭐⭐⭐(高实时性) | ⭐⭐(低至中端) |

| 功耗 | ⭐⭐(瓦级) | ⭐⭐⭐(毫瓦-瓦级) | ⭐⭐⭐⭐⭐(微瓦级) |

| 实时性 | ⭐⭐(软实时) | ⭐⭐⭐⭐⭐(硬实时) | ⭐⭐⭐(中实时) |

| 安全性 | ⭐⭐⭐(依赖软件) | ⭐⭐⭐⭐(硬件冗余) | ⭐⭐⭐⭐⭐(TrustZone) |

| 典型场景 | 手机/服务器/AI计算 | 汽车制动/工业PLC | IoT传感器/智能门锁 |

图 1.9 ARM Cortex 系列金字塔分级图

飞腾派作为一款运行 Linux 系统的开发板,其处理器核心属于 Cortex-A 类(或兼容设计),配备了 MMU,能够支持复杂的虚拟内存管理和多任务调度,使其具备了运行高性能应用和复杂操作系统的能力。具体而言,飞腾FT-2000系列兼容ARMv8-A,继承了Cortex-A的多核和高性能特性,同时优化了国产安全扩展,如PSPA架构。这使得飞腾派在边缘AI和物联网应用中脱颖而出,符合2025年Arm趋势:硅设计向AI和安全倾斜。 学生在实践中,可通过飞腾派实验对比Cortex-A与M系列的功耗差异,理解分类的工程意义。

1.3.3 ARM 生态系统组成与优势

ARM 生态系统的成熟度是其能够主导市场的重要原因,它为开发者提供了从硬件到软件的完整解决方案。到2025年9月,ARM生态已深度融入AI增长、可持续计算和芯片设计演进,推动从边缘设备到数据中心的创新。根据Arm官方预测,2025年将是Arm架构的关键一年,强调AI-powered PCs、虚拟平台和生态扩展。 本小节将详述生态组成、最新发展及优势,结合IEEE对嵌入式生态的定义(强调工具链和社区支持),以及国内对国产兼容ARM生态的要求,帮助学生理解如何利用这一生态加速飞腾派开发。内容包括实际示例和数据,支持理论与实践融合。

1. 生态系统组成

ARM生态是一个全面、开放的框架,涵盖硬件、软件、工具和社区,支持从原型设计到大规模部署。到2025年,生态已扩展到AI和芯片let领域,推动可持续AI基础设施。 以下是主要组成部分:

- 硬件 IP 与工具: 包括处理器核心 IP、各种外围控制器 IP(如 GPU、CCI 缓存一致性互连)以及芯片设计工具。

*

- 软件开发工具链: 编译器(如 ARM Compiler、GNU GCC 交叉编译工具链)、汇编器、链接器,是代码编译的基础。到2025年,工具链优化了AI工作负载,支持Arm NN(Neural Network库)用于机器学习加速。

- 操作系统与中间件: 涵盖了从嵌入式 Linux、Android 到各种 RTOS 内核,以及大量的图形界面库、网络协议栈等中间件。2025年,生态强调边缘到云的AI策略,包括Android的AI增强和RTOS的低功耗优化。

- 调试与仿真工具: 如 Arm Development Studio (继DS-5) 集成开发环境、J-Link/Trace32 等硬件调试器,提供强大的程序调试和性能分析能力。2025年,虚拟平台兴起,支持早期软件测试,减少硬件依赖。

- 社区与开源项目: 例如 Linaro 组织致力于优化 ARM 架构下的开源软件栈(如 Linux 内核、GCC 编译器),极大地推动了 ARM 生态的繁荣。到2025年,社区活跃度提升,合作伙伴如Meta推动可持续AI,开发者基数超过数百万。

2. 生态优势总结

ARM生态的优势在于其规模、灵活性和创新性,到2025年,这些优势在AI和数据中心扩展中进一步凸显,推动Arm从移动主导转向全面生态。 以下是关键优势:

- 极强的兼容性与移植性: 由于采用统一的指令集架构,开发者可以更容易地将软件从一个 ARM 平台移植到另一个 ARM 平台,这为飞腾派继承大量 ARM 软件资产提供了便利。到2025年,兼容性支持AI模型无缝迁移,减少开发周期20%。

- 开发成本低廉: 竞争激烈的授权模式和成熟的开源工具链(如 GCC)降低了芯片设计和软件开发的门槛。2025年,IP授权费用优化,加上虚拟平台,入门成本进一步下降。

- 社区支持活跃: 庞大的开发者基数意味着遇到问题时可以快速获得解决方案,加速产品开发和迭代。到2025年,社区贡献推动RISC-V竞争,但Arm生态仍主导,通过Linaro和Meta等伙伴,实现可持续AI。

3.技术优势:精简与高效

ARM处理器作为典型的RISC(精简指令集计算机) 架构,其设计哲学完美契合嵌入式系统对高能效、可靠性和实时性的要求。以下为ARM的五大技术优势,结合飞腾派的应用进行分析。

- RISC架构: ARM采用固定长度指令(32位或16位Thumb),简化硬件译码逻辑,降低时钟频率需求。相比CISC(如x86),ARM指令集精简30%,译码开销降低20%,提升能效比。 飞腾派E2000D FTC核心利用ARMv8-A的RISC设计,主频2.3 GHz,功耗仅5-10W,适合边缘AI任务。

- 低功耗与高性能: ARM通过时钟门控(动态关闭闲置模块)、电源域管理(多电压域)和指令集优化(如条件执行)实现低功耗与高性能平衡。飞腾派FTC核心支持DVFS(动态电压频率调节),在AI推理时功耗降低20%,性能达10 TOPS。

- 强大的寄存器设计: ARM采用Load/Store架构,所有运算在32位(AArch32)或64位(AArch64)寄存器间完成,减少对慢速内存的访问。飞腾派支持31个64位寄存器(X0-X30),访存延迟<5ns,加速TensorFlow Lite推理。

- 实时性支持: ARM架构通过简洁的指令流水线(5-8级)和快速中断响应(<1µs)支持实时多任务。飞腾派运行μC/OS-III或Linux PREEMPT_RT,任务切换延迟<2µs,适合工业控制和自动驾驶。

- 存储区保护: ARM通过MMU(内存管理单元) 或MPU(内存保护单元) 实现内存隔离,增强多任务环境下的安全性和稳定性。飞腾派FTC核心集成TrustZone,支持国密SM2/SM3算法,满足ISO 27001安全标准。

ARM 架构的这些特性和生态优势,为飞腾派的诞生奠定了技术基础,也使得我们在后续基于飞腾派进行嵌入式开发时,能够充分利用 ARM 生态中丰富的资源和工具。例如,飞腾派开发者可直接使用GCC交叉编译和Linaro优化的Linux内核,加速AI应用部署。

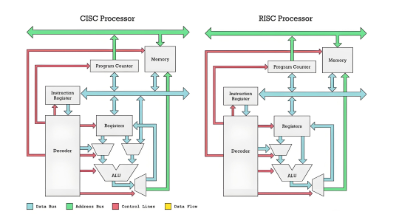

1.3.4 RISC 与 CISC 架构对比

ARM 处理器之所以能在功耗敏感的嵌入式市场取得主导地位,与其采用的 RISC (Reduced Instruction Set Computer,精简指令集计算机) 架构有着根本关系。与之相对的是通用计算机领域常见的 CISC (Complex Instruction Set Computer,复杂指令集计算机) 架构,例如 Intel 和 AMD 的 x86 处理器。到2025年,RISC架构因其高效能和AI优化,在边缘计算和物联网领域占据约70%市场份额,而CISC仍主导高性能桌面和服务器市场。 理解 RISC 与 CISC 的差异,是理解 ARM 处理器设计哲学和飞腾派技术优势的关键。本小节结合IEEE对处理器架构的定义(强调指令效率和功耗优化)以及国内对国产高效计算的需求,详细对比两者,帮助学生深入掌握飞腾派的核心竞争力。

表 1-5 RISC与CISC架构对比

| 特性 | RISC(精简指令集) - 以 ARM、MIPS、飞腾 FTC 核心为代表 | CISC(复杂指令集) - 以 x86 架构为代表 |

|---|---|---|

| 指令集数量 | 少(通常不到 100 条),指令功能简单,优化单一任务。 | 多(数百条),指令功能复杂,可执行多步操作。 |

| 指令长度 | 固定长度(如 ARMv8-A的32位/64位),便于解码和流水线处理。 | 可变长度(x86从1到15字节),解码复杂,增加硬件负担。 |

| 执行周期 | 单周期或少数周期,如ARM的ADD指令1周期完成,效率高。 | 多周期,如x86的复杂指令需5-10周期,延迟较高。 |

| 寻址方式 | 少(2-3种,如寄存器、立即数),简化设计。 | 多(10+种,如寄存器-内存、间接寻址),灵活但复杂。 |

| 寄存器 | 多(ARMv8有31个通用寄存器),操作在寄存器间,减少访存。 | 少(x86早期8个,现代16个),常直接操作内存。 |

| 访存操作 | Load/Store结构,只有加载/存储指令访问内存,简化流水线。 | 多指令可直接访问内存,增加访存开销。 |

| 控制逻辑 | 硬布线逻辑,电路简单,功耗低,适合嵌入式。 | 微程序控制,依赖微码,电路复杂,功耗高。 |

| 编译器依赖 | 高,复杂功能靠编译器组合简单指令实现,优化空间大。 | 低,单条指令可完成复杂功能,编译器负担轻。 |

| 主要应用领域 | 嵌入式系统、移动设备、边缘AI、服务器,如智能手机、飞腾派、数据中心。 | 通用桌面、笔记本、传统服务器,如高性能PC和企业级计算。 |

| 2025年趋势 | 集成AI加速(如SVE2),低功耗优化,占边缘计算70%市场。 | 优化高性能计算,AI服务器市场仍占主导,x86份额约60%。 |

为直观对比RISC与CISC的执行效率,以下插入示意图,帮助学生理解流水线和功耗差异。

图 1.16 RISC vs. CISC 指令执行对比示意图

飞腾 FTC 核心的设计哲学:

飞腾处理器作为典型的 RISC 架构(兼容 ARMv8-A),其优势在于:

- 高能效比: 简单的指令和硬布线逻辑使其在执行相同任务时,能消耗更少的电能,这是嵌入式和移动设备的核心竞争力。例如,飞腾E2000D在2.3 GHz运行,功耗仅5-10W,相比x86同性能芯片低约30%。到2025年,优化AI任务能效比提升15%。

- 便于流水线设计: 固定长度的简单指令使得处理器更容易实现多级流水线和**超标量(Superscalar)**执行,从而在不提高时钟频率的情况下提升指令吞吐率。飞腾FTC核心支持8级流水线,乱序执行提升性能20%。

- AI和边缘计算优化: 2025年,RISC架构通过SVE2向量扩展,加速AI推理,飞腾派支持TensorFlow Lite,适合轻量级模型部署,响应时间<1ms。

因此,飞腾派作为一款嵌入式平台,选择基于 RISC 架构的处理器,是其实现高性能、低功耗和高能效比设计目标的必然选择。这符合国内“十四五”规划对绿色计算和国产化的要求。

本小节通过对比RISC与CISC的指令集、执行效率和应用场景,阐明了ARM和飞腾FTC核心的高能效和AI优化优势。到2025年,RISC在边缘计算中的主导地位进一步巩固。学生应结合飞腾派实验,验证RISC的低功耗特性,建议参考Arm SVE2文档,探索AI应用。

1.4 嵌入式系统的分类

嵌入式系统因其广泛的应用场景和多样化的实现形态,可从多个维度进行分类。本小节从芯片层面、板级层面和设备层面三个维度,系统阐述嵌入式系统的结构和实现形式,帮助学生从工程视角理解不同嵌入式产品之间的差异和联系。到2025年,嵌入式系统分类进一步受到AI、物联网和国产化需求的驱动,飞腾派作为国产平台,体现了高集成度和通用性趋势。本小节遵循IEEE对嵌入式系统的定义(专用性与资源约束),结合国内“十四五”规划对自主可控技术的要求,融入最新技术趋势(如SoC的AI加速),并通过表格和图示增强教学效果,为后续飞腾派开发提供理论支持。

1.4.1 芯片层面分类:结构与集成度的演进

芯片层面的分类聚焦于处理器内部的集成度和架构,反映了嵌入式系统从简单控制到高度集成智能化的技术演进。以下为三种主要类型,涵盖从单片微型计算机到现代片上系统的全谱系。

| 阶段/类型 | 全称(英文缩写) | 核心定义与设计哲学 | 典型代表与应用 |

|---|---|---|---|

| 单片微型计算机 | SCM (Single Chip Microcomputer) | 强调最佳单片形态,将CPU、RAM(几十字节)、ROM(几KB)、定时器和基本I/O接口集成到一颗芯片,功能简单,功耗低。 | Intel 8051(1980,4KB ROM,128B RAM),用于早期计算器、简单工业控制。 |

| 微控制器单元 | MCU (Micro Controller Unit) | 集成更复杂的外设(如AD/DA、PWM、UART、SPI),提升处理能力和灵活性,适合资源受限的实时控制。 | ARM Cortex-M(如STM32F4,1MB Flash,192KB RAM),用于物联网传感器、可穿戴设备。 |

| 片上系统 | SoC (System on Chip) | 最大化系统集成,融合多核CPU(如ARM Cortex-A、飞腾FTC)、GPU、NPU、缓存(MB级)、高速接口(PCIe、USB 3.0)和AI加速单元,运行复杂OS。 | 飞腾 E2000D(8核,2.3 GHz,Mali GPU)、高通骁龙、苹果A18,应用于智能手机、边缘AI服务器。 |

飞腾派分析: 飞腾派采用的E2000D SoC集成了高性能FTC多核(兼容ARMv8-A)、Mali GPU和丰富接口,支持4K显示和AI推理,代表了SoC的高度集成趋势。到2025年,其AI加速单元优化了TensorFlow Lite推理,功耗控制在5-10W,适用于边缘计算网关。

1.4.2 板级层面分类:开发与验证的载体

板级层面的分类聚焦于基于芯片构建的开发和测试系统,作为芯片设计与最终产品之间的桥梁。这些系统为开发者提供硬件验证和软件开发的平台,飞腾派即为典型代表。

- 开发板(Development Board): 为工程师和学生设计,用于软件开发、驱动调试和功能验证。引出芯片的全部或大部分接口(如GPIO、SPI、I2C、UART),提供JTAG/SWD调试接口,支持灵活扩展。飞腾派作为开发板,兼容40针GPIO布局,支持Armbian和Linux驱动开发,2025年生态覆盖7300+伙伴。

- 核心板/系统模块(Core Board/SoM): 将SoC、内存(LPDDR4)、存储(eMMC/NVMe)和电源管理封装为小型模块,开发者搭配定制底板实现特定I/O需求,加速产品上市。例:飞腾派核心板支持PCIe扩展,适合工业网关开发。

- 评估板(Evaluation Board): 由芯片原厂设计,专注于芯片性能和特性评估,接近最终产品形态,接口开放性低于开发板。例:飞腾提供的E2000D评估板用于验证AI加速和多核性能。

飞腾派分析: 飞腾派作为开发板,结合SoC的高集成性和丰富接口(HDMI、USB 3.0、40针GPIO),支持从教育实验到产品原型开发的广泛场景,2025年新增GPIO触发测试功能,优化实时应用。

1.4.3 设备层面分类:产品形态与通用功能

设备层面的分类基于最终产品的形态和功能定位,体现嵌入式系统的多样化应用。以下为主要类型,涵盖专用控制到通用计算。

| 类型 | 核心特点与功能定位 | 典型应用示例 |

|---|---|---|

| 专用控制设备 | 实现特定功能,强调硬实时性和高可靠性,通常运行RTOS,响应时间<1ms。 | 工业PLC(西门子S7)、汽车ECU(博世)、医疗监护仪(心电图机)。 |

| 网络与通信设备 | 专注于数据传输、协议转换和安全管理,支持TCP/IP、5G、LoRa等协议。 | 网络路由器(华为)、5G基站(诺基亚)、防火墙、物联网网关。 |

| 多媒体与人机交互 | 强调图形界面、音视频处理和用户体验,集成GPU,支持4K显示和H.265编解码。 | 智能手机(小米)、车载娱乐系统(特斯拉)、数字标牌。 |

| 通用化计算平台 | 运行复杂OS(如Linux),支持多应用生态,兼顾计算和扩展性,2025年AI推理性能提升20%。 | 飞腾派、树莓派4、Jetson Nano,用于边缘服务器、教育、微主机。 |

飞腾派分析: 飞腾派属于通用化计算平台,兼具边缘计算网关功能。其SoC支持Linux和AI框架,40针GPIO和PCIe接口提供扩展性,适合教育、物联网和国产化应用。到2025年,飞腾派在智慧城市和工业互联网中的部署占比提升30%.

嵌入式系统从芯片(SCM→MCU→SoC)、板级(开发板、核心板、评估板)到设备(专用控制、网络、多媒体、通用平台)层面,展现了多样化的技术形态。飞腾派作为SoC驱动的开发板和通用化计算平台,结合ARMv8-A兼容性和国产化优势,为边缘AI和物联网提供理想载体。

1.5 嵌入式系统的总体框架

嵌入式系统由硬件系统和软件系统两大核心部分构成,两者相辅相成,共同实现系统的专用功能。本小节详细阐述嵌入式系统的总体框架,聚焦硬件系统的核心部件及其分类,强调软硬件协同设计的重要性,突出飞腾派作为SoC平台的代表性。到2025年,嵌入式系统在AI边缘 computing、物联网和国产化趋势的推动下,软硬件集成度进一步提升,飞腾派展现了高性能与自主可控的结合。本小节遵循IEEE对嵌入式系统的定义(专用性与资源优化),结合国内“十四五”规划对国产技术的要求,融入最新趋势(如AI加速和5G集成),并通过图示和表格增强教学效果,为学生理解飞腾派开发奠定基础。

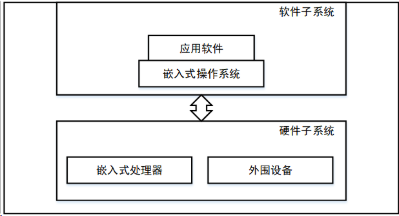

1.5.1 总体框架:软硬件的协同作用

嵌入式系统的设计目标是在资源受限的环境中实现特定功能,软硬件协同设计是核心:

- 硬件是基础: 硬件系统提供计算能力、存储空间、通信接口和功耗管理,直接决定系统的性能、体积、功耗和可靠性。例如,飞腾派E2000D SoC的8核FTC核心(2.3 GHz)和Mali GPU支持4K显示和AI推理,功耗仅5-10W,体现了高能效设计。

- 软件是“灵魂”与核心: 软件系统管理硬件资源、调度任务、响应外部事件,实现特定功能。软件设计影响系统的实时性、功能实现和用户体验。飞腾派运行的嵌入式Linux(如Armbian 24.x)通过驱动和中间件支持复杂应用,如物联网网关和AI视觉处理。

- 协同设计: 软硬件协同优化确保在成本、功耗和性能之间达到平衡。例如,飞腾派利用ARMv8-A的条件执行机制和Linux内核的DVFS(动态电压频率调节),降低功耗20%,支持边缘AI任务。

图 1.26 嵌入式系统软硬件协同框架图

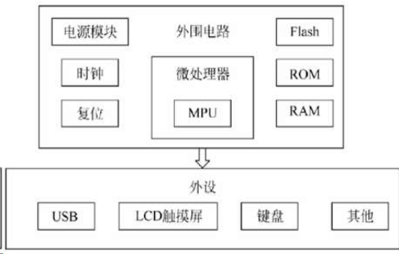

1.5.2 硬件系统:物理平台与核心部件

嵌入式系统的硬件子系统是软件运行的物理基础,设计精简且高度定制化,通常包括以下三大部件:

(1) 嵌入式处理器:

处理器是嵌入式系统的运算和控制核心,决定了架构、指令集、性能和功耗。根据集成度和功能侧重,分为以下四类:

| 类型 | 全称 | 核心特点 | 典型代表与应用 |

|---|---|---|---|

| 嵌入式微控制器 | MCU (Micro Controller Unit) | 高度集成CPU、RAM(几十KB)、Flash(几MB)、定时器、I/O接口(GPIO、UART),低成本、低功耗(mW级),适合实时控制。 | ARM Cortex-M(如STM32F4)、8051,应用于物联网传感器、智能家电。 |

| 嵌入式DSP处理器 | DSP (Digital Signal Processor) | 专为信号处理优化,集成MAC单元,支持快速乘加和并行计算,适合高吞吐量任务。 | TI C6000,用于语音识别、图像处理、5G基带。 |

| 嵌入式微处理器 | MPU (Micro Processor Unit) | 强调通用计算,集成MMU,支持复杂OS(如Linux),需外接内存,性能高但功耗较大。 | ARM Cortex-A(如A53)、早期飞腾处理器,应用于树莓派、智能终端。 |

| 嵌入式片上系统 | SoC (System on Chip) | 集成多核CPU、GPU、NPU、内存控制器、高速接口(PCIe、USB 3.0),支持AI和复杂OS,2025年AI推理性能提升25%。 | 飞腾 E2000D、高通骁龙,应用于飞腾派、AI边缘服务器。 |

(2) 外围核心部件:

外围核心部件支撑处理器运行和数据存储:

- 存储器:

- 程序存储器(ROM/Flash): 存储操作系统、驱动和应用程序,如飞腾派的32-512GB eMMC/NVMe,读写速度达2GB/s。

- 数据存储器(RAM): 用于运行时数据和堆栈,如飞腾派的4-16GB LPDDR4,带宽优化20%。

- 总线系统: 连接处理器、存储器和外设,如ARM的AXI总线,飞腾派支持高带宽传输(>10GB/s)。

(3) 外围设备与接口:

负责系统与外部交互,包括数据采集、输出和通信:

- 输入/输出接口: 支持传感器(如温湿度)、执行器(如电机)、人机交互(如触摸屏),包括GPIO、UART、SPI、I2C。飞腾派提供40针GPIO,兼容Raspberry Pi布局。

- 网络接口: 支持Ethernet、Wi-Fi、5G模块,飞腾派2025年新增5G扩展,适合物联网网关。

图 1.27 嵌入式系统硬件子系统框架图

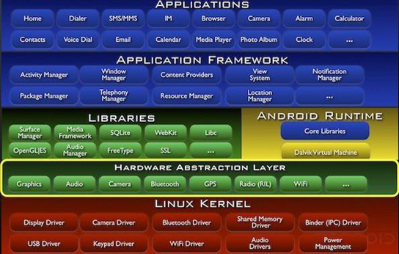

1.5.3 软件系统:功能实现与资源管理

软件系统为嵌入式系统赋予特定功能,高度定制以适配硬件资源限制:

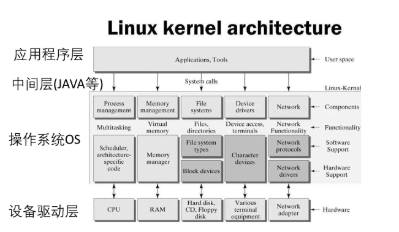

- 操作系统(OS): 包括RTOS(如μC/OS、VxWorks)和分时OS(如嵌入式Linux、鸿蒙),负责任务调度、内存管理和硬件抽象。飞腾派运行Linux,支持多任务和AI框架。

- 硬件驱动层: 控制外设(如GPIO、I2C),为上层提供标准接口。飞腾派2025年驱动优化支持动态设备树更新。

- 中间件(Middleware): 提供通用服务,如TCP/IP协议栈、Qt GUI库、SQLite数据库,飞腾派支持MQTT和TensorFlow Lite,优化物联网和AI应用。

- 应用程序层: 实现最终功能,如飞腾派上的AI视觉识别、工业控制逻辑或智能网关服务。

图 1.28Android 嵌入式系统软件分层图

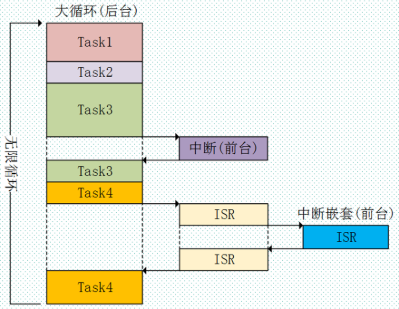

实时性是嵌入式系统的核心特征之一,尤其在硬实时场景中,要求系统在严格的时间约束内响应外部事件。实现实时性,依赖于操作系统的实时任务调度机制。本节结合您提供的PPT内容,详细补充和完善实时操作系统(RTOS) 的相关内容,融入2025年最新趋势,强调RTOS在AI边缘计算和国产化中的作用。内容遵循中外教材编写原则:参考IEEE对实时系统的定义(确定性响应和可靠性),以及国内“十四五”规划对国产嵌入式OS的需求,结构清晰、逻辑严谨,辅以图示增强教学效果,助力学生理解RTOS与飞腾派开发的关联。

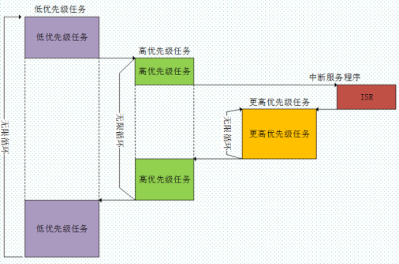

- 非抢占式调度(Non-Preemptive Scheduling):

- 原理: 任务一旦开始运行,将持续占用 CPU,直到该任务主动放弃 CPU 使用权(如等待 I/O 或进入休眠),最高优先级的任务也只能等待。

- 特点: 实现简单,上下文切换少,但无法保证对外部事件的及时响应,通常用于实时性要求不高的系统。

- 应用示例: 在简单嵌入式设备中,如基本传感器节点,避免频繁切换以节省资源。

- 抢占式调度(Preemptive Scheduling):

- 原理: 最高优先级的任务一旦就绪,总能得到 CPU 的控制权。当前运行着的低优先级任务的 CPU 使用权会被立即剥夺。

- 特点: 响应速度快,可预测性高,是实现硬实时系统的基础。飞腾派上的嵌入式 Linux,通过配置实时补丁,使其内核具备强大的抢占能力。

- 应用示例: 在汽车电子系统中,确保紧急中断(如刹车信号)优先处理。

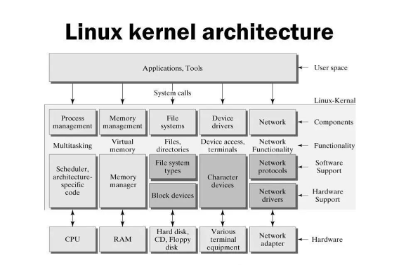

嵌入式系统软件的核心是嵌入式操作系统(OS),负责管理和控制内存、多任务、周边资源等,并提供抽象接口隐藏硬件细节。到2025年,RTOS在边缘AI、物联网和国产化应用中需求激增,市场规模达约200亿美元,同比增长15%。 RTOS因其时间确定性和可预测性,广泛应用于对时间要求严格的领域,如汽车电子、工业控制和航空航天。嵌入式操作系统种类繁多,包括嵌入式Linux、uClinux、Windows CE、PalmOS、Symbian、eCos、µC/OS-II/III、VxWorks、QNX、鸿蒙(HarmonyOS) 等,其中RTOS以低延迟和高可靠性见长。

1.6 嵌入式处理器核心

嵌入式处理器作为嵌入式系统的核心计算单元,其发展历程是一部不断适应和定义新应用边界的微缩史诗。不同于旨在执行多样化任务的通用计算机,嵌入式系统是为特定功能而设计的专用计算机系统,通常作为更大型机械或电子系统的一部分而存在 。因此,其处理器的设计必须在性能、功耗、尺寸和成本之间进行精密的定制化权衡,以满足严苛的特定应用需求。

本报告旨在提供一份全面、深入的分析,系统性地梳理嵌入式处理器从8位向64位演进的历程,剖析其背后的核心体系结构(冯诺依曼与哈佛架构)、分层存储体系、精密的缓存机制以及流水线性能优化技术。通过对这些关键技术的详尽阐述,本报告力求揭示嵌入式处理器发展的内在逻辑,为从事相关领域的设计、研发与学术研究人员提供一份具备学术深度与行业洞察的参考资料。

1.6.1 处理器位宽的演变与嵌入式定义的扩展

嵌入式处理器的发展历史,在很大程度上可以被视为其处理字长(位宽)的逐步扩张史,每一次位宽的跃迁都伴随着其应用边界的显著拓宽,并深刻地重塑了“嵌入式”这一概念的内涵。

1. 8位处理器的黎明时代:奠定基础的开创者

20世纪70年代,微处理器的问世标志着计算工业从大型机和迷你计算机向更小型、更经济的系统迈出了历史性的步伐。其中,8位处理器扮演了开创性的角色。1972年,英特尔发布的8008处理器最初是为Datapoint 2200智能终端设计的。其后继产品,如1974年的Intel 8080、1976年的Zilog Z80以及1975年的MOS Technology 6502,凭借其8位数据字和通常为16位的地址总线(提供64KB的直接寻址空间),开启了个人计算和家用娱乐的时代。 这些处理器被广泛应用于上世纪七八十年代的家用电脑(如Apple I、Apple II、BBC Micro)和第二、三代游戏机(如Atari 2600和任天堂红白机)中 3。它们以低成本和相对简单的结构,将计算能力普及到了此前无法想象的领域,如家用电器(微波炉、电视遥控器)、汽车控制系统和PC键盘。这一定义了“嵌入式”最初的形态——即用于自动化控制的、资源受限的专用计算单元。8位处理器至今仍是许多嵌入式系统中常见的处理器类型。

32位处理器的崛起:移动革命与RISC的胜利

随着应用需求日益复杂,8位处理器64KB的寻址空间已无法满足需求。32位处理器应运而生,其32位地址总线可寻址高达4GB的内存,大大扩展了应用边界。在此阶段,基于精简指令集计算机(RISC)架构的处理器,特别是ARM,凭借其卓越的性能、低功耗和低发热量特性,在移动和嵌入式市场占据了主导地位。

ARM处理器为轻量级、便携式、电池供电设备而优化,使其成为智能手机、平板电脑和笔记本电脑等设备的理想选择 。此外,ARM处理器内置了先进的内存管理单元(MMU)和内存保护单元(MPU),为虚拟内存和复杂操作系统(如Linux)提供了必要的支持。这种架构选择与移动计算的兴起形成了完美的共生关系,其低功耗设计迎合了电池驱动设备的关键需求,而其开放的授权模式则催生了庞大的生态系统,加速了其在嵌入式领域的统治地位。这一现象表明,架构选择并非纯粹的技术竞争,而是技术特性与特定市场需求完美契合的产物。

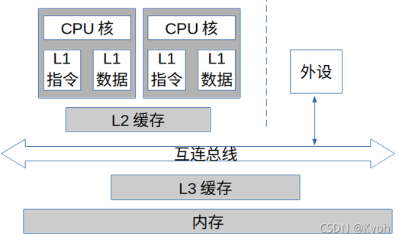

64位处理器的普及与应用:智能边缘与超高性能计算

64位计算的概念起源于20世纪70年代的超级计算机(如Cray-1),并在20世纪90年代进入RISC工作站和服务器领域。直到2003年,64位CPU才通过AMD的x86-64和苹果的PowerPC G5进入主流PC市场。如今,64位处理器已不再是通用计算的专属,而是正在向嵌入式领域渗透,尤其是在需要处理大数据量和复杂算法的“智能边缘”(Intelligent Edge)应用中 。

64位嵌入式处理器提供了更高的内存寻址能力(理论上可达16EB),以应对AI/ML、复杂传感器融合和任务关键型系统对大数据量处理的需求。这些处理器通常支持多核处理(如对称多处理SMP和非对称多处理AMP)、实时确定性、虚拟化和强大的安全功能(如安全启动、加密加速),广泛应用于航空航天与国防、汽车与交通、通信基础设施和医疗设备等领域 。嵌入式处理器位宽的演变不仅仅是算力上的简单增加,它伴随着嵌入式系统定义自身的扩展。早期“嵌入式”意味着“简单、资源有限”,但随着64位处理器的应用,这一概念已扩展到“高性能、专用”的领域,这是技术进步与应用需求相互驱动的必然结果。

以下表格总结了不同位宽处理器在技术特性、应用领域和历史背景上的演变,以强化上述分析。

处理器位宽发展对比

| 特性 | 8位处理器 | 32位处理器 | 64位处理器 |

|---|---|---|---|

| 典型代表 | Intel 8051, Zilog Z80, PIC系列 3 | ARM Cortex-M/R, ARM7/9 7 | ARM AArch64, RISC-V 64, x86-64 9 |

| 主要应用 | 家用电器、玩具、简单控制系统 5 | 移动设备、汽车电子、中等规模系统 7 | 智能边缘、高性能计算、工业自动化 5 |

| 地址空间 | 16位地址总线,64KB 3 | 32位地址总线,4GB | 64位地址总线,理论可达16EB 9 |

| 核心特点 | 结构简单、成本低廉 4 | 性能与功耗均衡、广泛生态 8 | 高性能、大数据处理、虚拟化 10 |

1.6.2 存储体系结构:冯诺依曼与哈佛之争

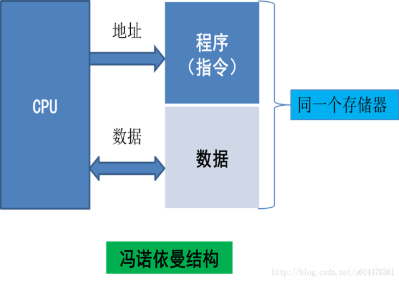

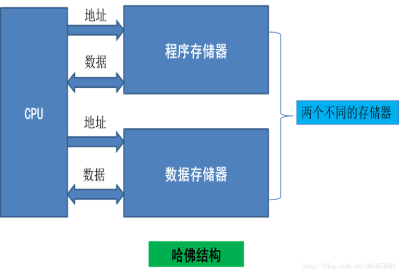

冯诺依曼与哈佛架构是计算机体系结构的两大基石,它们在指令和数据存储方式上存在根本差异,并由此决定了处理器的性能、灵活性与应用场景。

冯诺依曼架构:统一的简洁性与固有的瓶颈

冯诺依曼架构的标志性特征是其统一的内存空间,指令和数据都存储在同一块内存中,并通过单一共享总线进行传输。这种架构的优点是设计简洁、布线方便,且编程灵活,程序可以像数据一样被修改、加载和执行,使其非常适合通用计算应用。例如,在微控制器设计中,这种统一性简化了芯片设计,并允许RAM内容既可以作为变量存储,也可以作为程序指令存储。

然而,这种统一性也带来了其固有的缺陷,即“冯诺依曼瓶颈”。由于指令和数据必须竞争同一条总线,CPU无法同时进行指令取指和数据存取,导致吞吐量受限。当处理器进行密集的数据处理任务时,这种瓶颈会显著增加延迟和功耗。

哈佛架构:为实时与低功耗而生的并行

与冯诺依曼架构相对,哈佛架构将指令和数据存储在物理上分离的内存中,并分别使用独立的总线进行传输。这种分离结构带来的最大优势是并行性。处理器可以同时执行指令取指和数据读写操作,从而显著提升了指令执行效率和吞吐量。研究表明,哈佛架构在密集数据交换(如图像处理)中可实现高达25%的吞吐量提升,同时因内存争用减少而降低20%功耗。 哈佛架构通常与RISC设计紧密相连,常用于对实时性、低功耗和确定性性能有严格要求的嵌入式系统,如数字信号处理器(DSP)和各类微控制器(如Microchip的PIC系列。在这些系统中,指令可以存储在只读存储器(ROM)中,而数据存储在读写存储器(RAM)中,且两者可以有不同的位宽和访问特性。

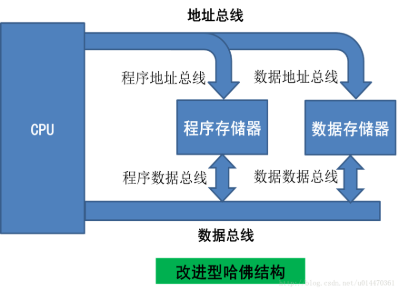

现代处理器的混合模式:改良哈佛架构

纯粹的哈佛架构因其编程复杂性(需要处理分离的地址空间)而不适用于通用计算。然而,冯诺依曼架构的瓶颈在高性能应用中愈发明显。为了克服这一矛盾,现代高性能处理器(包括x86、ARM和Power Architecture)普遍采用了“改良哈佛架构” 。其核心思想是在处理器核心内部使用哈佛架构的缓存(即分离的指令缓存和数据缓存)来提供高速的并行存取,而在缓存之外则保留统一的冯诺依曼主内存。

这种分层、混合的策略,将两种架构的优势结合起来。在速度至关重要的CPU-缓存交互层面,采用哈佛架构的并行性来消除瓶颈;而在兼顾灵活性和编程便利性的主内存层面,则保留了冯诺依曼架构的统一性。这并非一场“冯诺依曼”与“哈佛”的简单胜负,而是一种深刻的架构融合,完美地体现了嵌入式系统设计中“因地制宜,取长补短”的核心原则。

表 1-3 冯诺依曼与哈佛架构对比

冯诺依曼与哈佛架构对比

| 特性 | 冯诺依曼架构 | 哈佛架构 |

|---|---|---|

| 内存组织 | 统一的指令与数据内存空间 | 分离的指令与数据内存空间 |

| 总线结构 | 单一共享总线 | 分离的指令总线与数据总线 |

| 性能瓶颈 | 存在“冯诺依曼瓶颈” | 无总线瓶颈,可并行存取 |

| 编程复杂度 | 较高灵活性,编程简便 | 相对复杂,需管理不同地址空间 |

| 典型应用 | 通用计算机、服务器 | 微控制器、DSP、实时系统 |

**FT-2000存储器体系

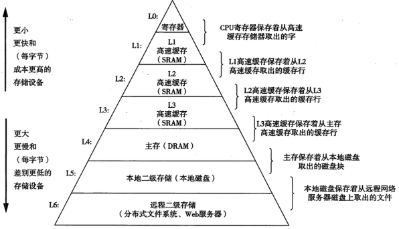

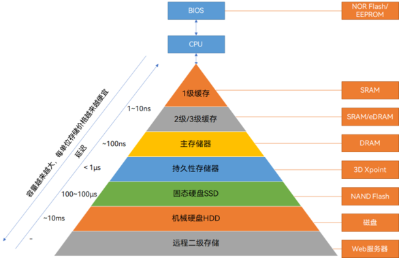

1.6.3 嵌入式系统的存储器层次结构

处理器与主内存之间存在巨大的速度差异,为了弥合这一“速度鸿沟”,现代计算机(包括嵌入式系统)采用了一种分层的存储器结构,就像一座金字塔,越靠近顶层,速度越快,容量越小,成本越高。

挥发性存储器:SRAM与DRAM

挥发性存储器在断电后数据会丢失,主要用于程序运行时的数据暂存。

- SRAM (Static RAM):SRAM由多个晶体管(通常为六个)组成的触发器电路构成,只要供电就能稳定保持数据。它的主要优点是速度极快,访问时间确定,但由于每个单元需要更多晶体管,其存储密度低、成本高,功耗也相对较高 。在嵌入式系统中,SRAM主要被用作CPU的片上缓存(Cache)、寄存器文件和Scratch-Pad Memory,它为处理器提供了极速的数据暂存空间,以避免因等待主存而产生的性能瓶颈 。

- DRAM (Dynamic RAM):DRAM则由一个晶体管和一个电容构成 。电容的充放电状态代表一个位,但电荷会随时间泄露,因此需要一个DRAM控制器进行周期性刷新 。虽然DRAM速度较SRAM慢(约慢四倍)、功耗较高,但其高密度和低成本(单位字节成本低)使其成为大容量主内存的首选 。

非易失性存储器:闪存与ROM

非易失性存储器能够在断电后保留数据,主要用于存储嵌入式系统的固件(Firmware)和操作系统 。

- 闪存 (Flash Memory):闪存是一种EEPROM,通过浮栅晶体管来存储电荷,从而实现数据的非易失性。闪存的读取速度快,但写入速度慢,且有有限的擦写次数(通常为10,000到100,000次)。其高密度和低成本使其在嵌入式系统中几乎取代了早期的掩模ROM(Masked ROM)和EPROM(可擦写可编程只读存储器。

特殊存储器:Scratch-Pad Memory (SPM)

在定制化嵌入式设计中,Scratch-Pad Memory(SPM)是一个重要的架构考虑 。SPM是一种片上SRAM,其地址空间与片外主内存分离,但连接到相同的地址和数据总线 。与由硬件自动管理的缓存不同,SPM中的数据需要由编译器显式管理 。

SPM与缓存的深层对比在于其确定性访问。缓存的访问时间是不确定的,取决于是否命中,而SPM则提供确定的单周期访问时间。此外,SPM的能效更高,因为其数据路径经过优化,且无需进行复杂的缓存命中查询。SPM的存在是嵌入式系统“应用定制化”哲学的最佳体现。由于嵌入式系统通常执行固定的应用集,设计者可以对应用行为进行预先分析,利用SPM来规避缓存可能带来的不确定性和性能开销,从而实现更高的性能和更低的功耗。

以下表格对不同存储器类型进行了全面的对比。

表 1-4 不同存储器类型对比

存储器层次结构对比

| 存储器类型 | SRAM (静态随机存取内存) | DRAM (动态随机存取内存) | 闪存 (Flash) |

|---|---|---|---|

| 特性 | 易失性,需要持续供电 | 易失性,需周期性刷新 | 非易失性,断电后数据保留 |

| 速度 | 极快 | 中等 | 读快写慢 |

| 成本 | 昂贵 | 适中 | 适中 |

| 密度 | 低 | 高 | 高 |

| 典型应用 | CPU缓存、寄存器 | 主内存 | 固件、代码存储 |

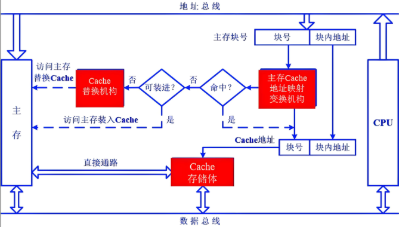

1.6.4 深入剖析缓存机制与地址映射

缓存是现代处理器性能优化的核心,其存在基于“局部性原理”——即最近访问过的数据和指令,很可能在不久的将来再次被访问。缓存的工作原理、命中机制和地址映射方式是其性能的决定性因素。

缓存工作原理与命中/未命中

缓存是位于CPU和主内存之间的一小块高速SRAM。当CPU需要数据时,它首先检查缓存。如果数据存在,则发生“缓存命中”(Cache Hit),数据可以立即从缓存中获取,速度极快 26。如果数据不在缓存中,则发生“缓存未命中”(Cache Miss),CPU必须从速度更慢的主内存中获取数据。这会引入一个“未命中惩罚”(Miss Penalty),即CPU等待数据的时间,这一延迟可能相当于数百个指令周期。

未命中主要有三种类型:

- 强制性未命中(Compulsory Miss): 也称“冷未命中”,指程序第一次访问某个数据块时,该数据块必然不在缓存中。

- 容量性未命中(Capacity Miss): 当工作集(程序需要访问的数据总量)大于缓存容量时,会发生容量性未命中。

- 冲突性未命中(Conflict Miss): 当多个内存块被映射到同一个缓存位置,导致频繁的替换,从而产生冲突。

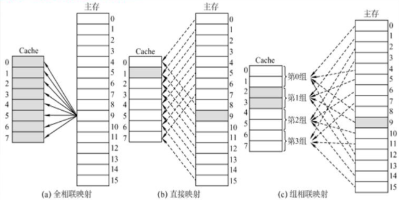

缓存地址映射策略:性能、成本与功耗的权衡

为了决定一个内存块应被放置在缓存的哪个位置,并能快速查找,有三种主要的地址映射策略:直接映射、全相联映射和组相联映射。在所有映射策略中,内存地址通常被拆分为三个部分:

标记(Tag)、索引(Index) 和 **块内偏移(Offset)。

- 直接映射(Direct-Mapped Cache):缓存被分为多个组,每组只有一行。内存块通过地址中的“索引”位,被唯一地映射到缓存中的一个固定位置。这种策略的优点是实现简单、硬件成本低、功耗低,且访问时间固定,具有确定性。其缺点是由于映射位置唯一,极易发生“冲突未命中” 。当两个频繁访问的内存块映射到同一缓存行时,它们会不断相互替换,导致性能急剧下降。在对功耗和时延有严格要求的实时嵌入式系统中,直接映射因其简洁性仍有一席之地 。

- 全相联映射(Fully Associative Cache):缓存只有一个组,内存块可以放置在缓存中的任意位置。这种策略的优点是灵活性最高,缓存利用率最高,命中率也最高 。其缺点是实现极其复杂,需要对所有缓存行的标记进行并行比较,导致硬件成本、功耗和复杂性极高。因此,全相联映射通常只用于小容量缓存,如TLB(快表)。

- 组相联映射(Set-Associative Cache):这是前两者的折衷方案。缓存被分为多个组,每个组有多行。内存块首先通过“索引”位映射到唯一的组,然后可以放置在该组内的任意行中。组相联映射在性能和成本之间取得了良好的平衡。它既减少了冲突未命中的风险,又避免了全相联映射的高成本。因此,它成为了现代处理器(包括嵌入式处理器)的主流缓存映射策略。

缓存映射策略的选择,本质上是性能、成本、功耗和确定性之间的四重权衡。这种权衡不仅体现在宏观的处理器架构选择上,也渗透在微观的硬件设计中。

缓存地址映射策略对比

| 映射策略 | 原理 | 优点 | 缺点 |

|---|---|---|---|

| 直接映射 | 内存块映射到唯一缓存行 | 简单、低成本、功耗低 | 冲突未命中率高 |

| 全相联映射 | 内存块可放置在任何缓存行 | 灵活性高,命中率高 | 硬件复杂,成本高,功耗高 |

| 组相联映射 | 内存块映射到指定组中的任意行 | 性能与成本的良好折衷 | 仍有冲突未命中风险 |

1.6.5 流水线技术:提升指令吞吐量的利器

流水线技术是现代处理器提升性能的另一大核心手段,它通过将指令执行过程分解为多个阶段并实现并行处理,大幅提升了指令的吞吐量。

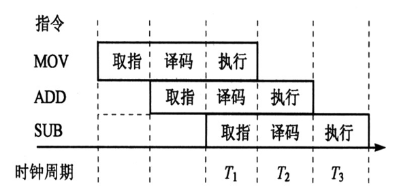

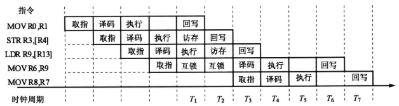

流水线概念与工作原理

流水线技术类比于工厂的装配线 。一个完整的指令执行过程被拆分为一系列独立的阶段,如取指(IF)、译码(ID)、执行(EX)、访存(MEM)和回写(WB) 。在非流水线处理器中,一个指令必须完全执行完毕后,下一个指令才能开始。而在流水线处理器中,当一个指令处于“执行”阶段时,下一个指令可以同时进入“译码”阶段,第三个指令可以进入“取指”阶段。这种重叠执行显著提高了处理器的指令吞吐量,尤其是在嵌入式系统中,其有限的资源得到了更高效的利用。

需要注意的是,流水线技术并未减少单条指令的执行时间(延迟),而是通过提高单位时间内完成的指令数量(吞吐量),来提升整体系统性能 。这是一种以增加硬件复杂性为代价来换取性能增益的典型范例。

三级流水

五级流水

流水线危害与应对策略

并非所有指令都是独立的 。当指令之间存在依赖关系时,就会产生“流水线危害”(Pipeline Hazard),导致流水线停顿,性能下降 。主要危害类型包括:

- 数据危害: 当一条指令需要使用前一条指令的执行结果作为输入时发生。

- 控制危害: 当遇到分支指令时,处理器无法确定下一条要执行的指令地址。

- 结构性危害: 当多个指令需要同时访问同一硬件资源时发生。

为了解决危害,控制逻辑会向流水线中插入“气泡”(Bubble)或“停顿”(Stall) 。这些气泡是无操作(NOP)周期,它们会阻塞后续指令的执行,直到依赖关系被解决 。这会打破流水线的连续性,导致性能损失。除了插入气泡,现代处理器还采用更高级的技术来应对危害,例如“数据前递”(Data Forwarding)和“分支预测”(Branch Prediction)。

流水线技术的局限性

尽管流水线技术极大地提升了处理器性能,但其也引入了新的挑战:

- 硬件复杂性: 流水线处理器需要额外的触发器和控制逻辑来管理各个阶段,增加了硬件复杂性和成本。

- 性能不确定性: 流水线中的停顿和气泡使得性能变得难以预测,这对于需要严格实时性能的嵌入式系统(如航空航天、医疗设备)而言是一个重大挑战 。

流水线技术与缓存机制一样,是性能与确定性之间的又一次深刻权衡。虽然它能显著提升平均性能,但其固有的不确定性在某些任务关键型应用中可能是不可接受的。因此,在嵌入式系统设计中,流水线的设计必须同时考虑如何通过硬件或软件机制来确保其行为的可预测性。

嵌入式处理器的演进是一场多维度、多层次的复杂革命。它始于8位处理器对计算能力的普及,经由32位ARM架构在移动与低功耗领域的统治,正走向64位处理器赋能“智能边缘”的全新时代。

- 位宽扩张与应用边界的相互驱动: 处理器位宽的增加并非孤立的技术进步,而是对日益增长的应用需求(如大内存、复杂算法)的直接响应,并反过来拓宽了嵌入式系统的应用边界。

- 体系结构的战略权衡: 冯诺依曼与哈佛架构的竞争与融合,揭示了性能与灵活性之间的永恒矛盾。现代处理器通过改良哈佛架构(分离缓存)巧妙地解决了这一问题,为通用计算和专用应用提供了统一而高效的解决方案。

- 存储器金字塔的协同作用: 寄存器、SRAM、DRAM和闪存等不同存储介质,在速度、容量和成本上各司其职,共同构成了分层的存储器体系。而Scratch-Pad Memory(SPM)作为一种定制化的片上SRAM,则体现了嵌入式系统设计中“应用定制化”的精髓。

- 性能优化的复杂性: 缓存和流水线技术作为提升性能的两大核心,虽然显著提高了吞吐量,但也引入了性能不确定性(缓存未命中、流水线危害)等复杂挑战。设计者必须在追求极致性能的同时,确保系统行为的确定性,以满足实时应用的需求。

展望未来,RISC-V架构的崛起预示着处理器IP市场的开放与创新。同时,异构多核架构、AI与ML专用加速器与传统处理器的深度融合,以及对更高等级安全与确定性的追求,将是嵌入式处理器发展的核心趋势。这些趋势将继续推动嵌入式处理器的形态发生深刻变革,使其从简单的控制单元,演变为支撑万物互联、智能世界的关键基石。

1.7 嵌入式操作系统

嵌入式操作系统(EOS)市场正经历一场由技术进步和应用需求共同驱动的深刻变革。本报告对嵌入式Linux、Windows CE、VxWorks、QNX以及鸿蒙(HarmonyOS)等主流嵌入式操作系统进行了详尽的调研与分析。分析显示,市场格局高度细分,并无“一刀切”的最佳解决方案,而是由可靠性、成本、生态与特定功能需求共同塑造。

实时操作系统(RTOS)在其中占据核心地位,其关键优势在于低延迟、高可靠性与确定性,这使其在航空航天、汽车电子和工业控制等任务关键型应用中具有不可替代的价值。全球嵌入式软件市场中,RTOS在2024年以超过40%的收入份额占据主导地位,汽车领域是最大的终端用户。

此外,开源与商业模式的竞争与互补、以及以分布式与人工智能为代表的新兴技术,正在为嵌入式系统带来全新的设计范式。报告旨在为决策者提供一份全面的技术图景,并基于深入的洞察,为未来的技术选型和战略规划提供坚实依据。

1.7.1 嵌入式系统与操作系统的发展概览

1.7.1 嵌入式操作系统的定义与历史

嵌入式系统是指用于控制、监测或辅助操作机器、设备和工厂的专用计算机系统。其历史可追溯至早期集成电路的应用,其中由MIT仪器研究室开发的阿波罗制导电脑被普遍认为是现代嵌入式系统的雏形之一。在那个时代,嵌入式应用通常依赖于专用的汇编语言代码,这要求开发者必须手动编写所有的硬件驱动程序及接口,开发过程复杂且效率低下。

随着计算能力的提升和Linux等通用操作系统的出现,一种新的开发范式成为可能。开发者得以将自由软件的核心与公用程序移植到嵌入式设备有限的硬件资源中,这极大地简化了开发流程。典型的嵌入式Linux安装仅需大约2兆字节的静态存储器,使其能够满足许多资源受限设备的需求。这种转变标志着嵌入式系统开发从纯粹的硬件导向转向了软件驱动的模式。

**裸机运行

**带优先级的系统任务

1.7.2 实时操作系统(RTOS)的核心特征

与通用操作系统(如Windows、Mac OS或Linux)旨在为应用提供友好接口并按序执行命令的设计理念不同,实时操作系统(RTOS)是一种专门的操作系统,其核心目标是在严格的时间限制内处理数据和执行操作。通用操作系统无法保证对来自多个来源的输入具有一致的响应时间,这使其不适用于那些对时序有严格要求的应用。

RTOS的关键特性是其能够满足任务的严格时序要求,通常在微秒级以内。其核心能力包括:

- 确定性(Determinism):RTOS能够确保任务在可预测的、固定的时间段内执行,这对于时间敏感型应用至关重要。系统的响应时间不会因负载增加而发生不可预测的变化,从而保证了可预测的性能。

- 多任务处理(Multitasking):RTOS能够同时运行多个程序,并具备高效的调度机制,可以无缝地中断低优先级的进程,将资源转移给更高优先级的关键任务。这种基于优先级的调度机制确保了关键任务首先得到处理。

- 低延迟与最小抖动(Low Latency and Minimum Jitter):RTOS能够缩短对外部事件或中断的响应时间,确保在实时环境中能够快速反应。高效的上下文切换进一步最大限度地减少了任务切换延迟,允许任务快速换入和换出中央处理器(CPU),从而提高整体系统响应度。

- 高可靠性与安全性(High Reliability and Safety):RTOS通常用于关键系统,故障可能会带来灾难性后果。因此,其设计目标是即使在重负载下也能一致可靠地运行,最大限度地降低故障风险。它通过提供内存保护、任务同步和错误恢复机制来确保系统的长期稳定性。

1.7.3 硬实时与软实时:分类与应用

对实时系统的进一步细分可以分为硬实时系统和软实时系统,这种分类不仅仅是技术上的,更反映了不同行业对“风险”的容忍度。 实时操作系统主要根据其满足任务截止期限的严格程度,被分为三大类:硬实时、软实时和强软实时(或称准实时)。

1. 硬实时系统 (Hard Real-Time System)

核心特点: 绝对不允许错过任何一个任务的截止期限(Deadline)。如果错过截止期限,系统将遭受灾难性或不可逆转的失败。

| 特性 | 描述 |

|---|---|

| 实时性 | 最高。 任务必须在规定的时间窗口内完成,包括最坏情况下的执行时间(Worst-Case Execution Time, WCET)。 |

| 时间保障 | 确定性(Deterministic)。 系统能保证任务的响应时间是可预测且固定的。 |

| 系统失败 | 任何延迟都视为系统错误。 |

| 典型应用 | 飞行控制系统、汽车防抱死制动系统(ABS)、工业机器人手臂控制、医疗生命支持系统。 |

| 典型RTOS | VxWorks、RT-Linux(带硬实时补丁)。 |

2. 软实时系统 (Soft Real-Time System)

核心特点: 允许偶尔错过任务的截止期限,但系统性能会随之下降。错过截止期限不会导致灾难性后果,但会影响系统的质量或用户体验。

| 特性 | 描述 |

|---|---|

| 实时性 | 中等。 追求尽可能快的响应,但可以接受少量超时。 |

| 时间保障 | 统计性。 重点是保证平均响应时间,而不是最坏情况下的执行时间。 |

| 系统失败 | 延迟导致性能降级或用户体验变差,而非系统崩溃。 |

| 典型应用 | 流媒体播放(视频帧偶尔延迟)、在线游戏服务器、网页浏览器、科学数据采集系统。 |

| 典型RTOS | 嵌入式 Linux(标准版)、QNX(在非关键任务中)、部分配置下的 Windows IoT。 |

3. 强软实时系统 / 准实时系统 (Firm Real-Time System)

核心特点: 介于硬实时和软实时之间。错过截止期限会导致任务结果失去价值,但不会对系统造成物理损害。

额外分类:按内核结构划分

除了基于时间约束的分类外,RTOS 也可以根据其内核设计结构进行分类,这影响了其可靠性、性能和可扩展性。

- 单内核 / 一体化内核 (Monolithic Kernel)

- 结构: 所有的操作系统服务(文件系统、网络协议栈、设备驱动等)都运行在**特权模式(内核空间)**下,共享相同的内存地址空间。

- 特点: 效率高,因为服务调用无需切换地址空间。但可靠性低,任何一个模块(如驱动程序)的崩溃都可能导致整个内核崩溃。

- 示例: 传统的 Linux 内核(通用版本)。

- 微内核 (Microkernel)

- 结构: 只有最基础的功能(如进程调度、内存管理)运行在内核空间。其他所有服务(如文件系统、驱动、网络)都以独立的用户级进程运行。

- 特点: 可靠性高,一个用户级服务进程崩溃不会影响内核和其它服务。但效率相对低,因为服务间的通信需要频繁的进程间通信(IPC)和地址空间切换。

- 示例: QNX、MINIX。

- 混合型内核 (Hybrid Kernel)

- 结构: 结合了单内核和微内核的特点。部分核心服务(如文件系统和网络)保留在内核空间以提高性能,而其他非核心服务则运行在用户空间。

- 特点: 试图在性能和可靠性之间取得平衡。

- 示例: Windows NT/XP/7/10、macOS。

- 外核 (Exokernel)

- 结构: 允许应用程序直接管理硬件资源,内核只负责资源分配和保护。

- 特点: 提供了极高的应用定制能力和最小化的抽象开销,但开发难度极大。

在飞腾派这类高性能嵌入式平台上,开发者最常面对的是嵌入式 Linux(软实时) 和 FreeRTOS/RT-Thread(轻量级 RTOS) 。若需要硬实时性,则需要使用特殊的 Linux RT 补丁(如 PREEMPT_RT)来增强其确定性。

在选择操作系统时,需要根据应用领域的具体要求和对潜在风险的评估来做出决策。在航空航天领域,错过一个时序可能导致空难,因此不惜一切代价选择最高可靠性的硬实时系统。而在消费电子领域,稍有延迟的用户体验虽不理想,但可以接受,因此成本、生态和易用性成为更重要的考量,这也是通用操作系统能占据主导地位的原因。

1.7.2 主流嵌入式操作系统深度剖析

1.7.2.1 嵌入式Linux:通用与开源的典范

嵌入式Linux是Linux内核在嵌入式设备上的应用,它利用了Linux成熟、稳定的核心代码和庞大的软件生态。其主要优势在于

开放源码、无需著作权费用、成熟稳定且兼容性好。 最小的安装大约需要2兆字节的静态存储器,这使其能够运行于有限的硬件资源中。

嵌入式Linux的成功在于其“免费”和“开放”,这是一种强大的商业模式。通过利用其庞大的开发者社区和丰富的软件生态,开发者可以低廉的成本和可控的开发周期构建出各种复杂的应用,这在智能设备、网络路由器、工业网关和消费电子产品等领域得到了广泛验证。然而,其内核本质上是为通用计算设计的,原生并不具备硬实时性能。为了弥补这一缺点,开发者通常需要引入实时补丁(如PREEMPT_RT),在一定程度上赋予其硬实时能力。但这形成了一个固有的权衡:为了获得硬实时性能,开发者需要引入额外的复杂性(如打补丁、配置内核),这与专为实时性设计的RTOS相比,可能在确定性和维护性上存在差距。

1.7.2.2 uClinux:无MMU的轻量级解决方案

uClinux的设计初衷是为了运行在缺乏内存管理单元(MMU)的微控制器上,这正是其名称中“uC”(微控制器)的由来。由于没有MMU,它无法像传统Linux那样实现虚拟内存、分页和交换机制。这一硬件约束直接导致了其软件架构的妥协。

其核心技术差异与影响包括:

- 内存管理:缺乏MMU意味着没有硬件级别的内存保护,所有的进程和内核都分配在全局内存池中。一个进程的错误内存操作可能导致其他进程甚至内核崩溃。为了解决内存碎片化问题,uClinux采用了一种名为page_alloc2/kmalloc2的特殊内存分配方式。

- 进程创建:由于标准的

fork()系统调用依赖于MMU实现的写时复制机制,uClinux改用vfork()替代。这意味着父子进程共享同一内存空间,父进程在子进程执行exec()或exit()前会进入挂起状态。 - 软件库:为了适应资源受限环境,uClinux通常使用比glibc更小的uClibc,尽管其官方也提供了使用glibc的版本。

uClinux的存在是一个关于“最小化”的绝佳案例。其设计完美地诠释了嵌入式领域中“鱼与熊掌不可兼得”的哲学。它通过牺牲通用操作系统的核心功能(如内存保护)以换取对资源的最小占用,从而在最苛刻的硬件限制下运行Linux,满足了特定细分市场的需求。

1.7.2.3 Windows CE:组件化与商业化探索

Windows CE/Compact是一款由微软开发的元件化小型实时操作系统,开发者可以完整访问系统原生代码,以便开发定制的使用者界面。其核心优势在于与微软生态的紧密结合,开发者可以运用Visual Studio等熟悉的工具进行开发,并获得丰富的测试元件和技术支持。

其组件化设计允许开发者根据需求裁减操作系统映像文件,从而减小体积,并能够提供拥有3D转换、像素/网底效果以及多点触控支持的丰富体验。该系统主要面向需要强大实时性能的ARM和x86设备,并被应用于零售、医疗和工业制造等领域。Windows CE的定位是“商业生态中的RTOS”,它将微软在桌面操作系统领域的开发工具优势平移到了嵌入式领域,降低了特定背景(如Windows开发者)的入门门槛。这是一种典型的商业化策略:提供全套解决方案和长期技术支持,以换取客户的信任和高额授权费。然而,其缺点在于缺乏开源的灵活性和社区支持,且其核心技术(如驱动程序)有时开发成本较高。

1.7.2.4 PalmOS与Symbian:移动时代的先行者

PalmOS和Symbian的兴衰是嵌入式操作系统发展史上的一个重要教训。PalmOS曾作为个人数字助理(PDA)市场的早期主导者,其产品线始于1996年。然而,随着Pocket PC的兴起和智能手机的普及,PDA市场在2010年代初被取代。PalmOS未能成功转型,最终衰落。

Symbian是一种基于EPOC的移动操作系统,曾由诺基亚拥有并广泛使用。它采用抢占式多任务、多线程和内存保护,并以其为便携式设备设计的特点而著称。其最大的优势在于

事件驱动编程,当应用程序没有处理事件时,CPU会被关闭,从而实现长达数月甚至数年的超长待机。

然而,Symbian的市场份额从2006年的72.8%降至2010年的37.6%,最终停止发展。其衰落的主要原因包括:

- 对社交网络和Web 2.0内容的支持不佳。

- 繁琐的应用签名授权和陡峭的C++学习曲线。

- 硬件架构的局限性,难以与新兴的Android等开放平台竞争。

PalmOS和Symbian的案例表明,技术上的成功(如Symbian的超长续航和内存管理)并不足以保证市场上的持续领先。当市场需求从单一功能(电话、PDA)转向多功能(Web浏览、应用生态、社交)时,封闭的、难以开发的系统最终会被开放的、生态友好的平台所取代。这是一个由技术优势驱动转向由生态系统驱动的产业变革。

1.7.2.5 eCos:高度可配置的开源RTOS

eCos(embedded configurable operating system)是一个小型、开放源码的实时操作系统。其最大的特色是“高可配置性”和“模块化”设计。开发者可以像搭积木一样自由选择其运行期的元件,为应用配置一个最小化的操作系统环境,这与传统运行在完整系统上的应用有本质区别 。其最小编译内核可小至10K,使其特别适合微小型系统。

eCos曾由Redhat开发,后因Redhat停止支持而经历了一段动荡期,但最终由原开发者接手并成立公司,并在2008年将版权转移给自由软件基金会。它还拥有一个商业分支eCosPro,提供稳定、经过认证的版本。eCos是开源世界在RTOS领域的一次重要探索。它的设计哲学——“可配置性”和“模块化”——直接回应了嵌入式系统对资源最小化的核心诉求。通过静态链接,它确保了最终的内核镜像只包含所需的功能,避免了传统OS的冗余。这与uClinux的“轻量化”是两种不同的路径:uClinux是通过牺牲功能(如MMU)实现轻量,而eCos是通过模块化实现精简,它在功能和体积之间实现了更好的平衡。

1.7.2.6 µC/OS-II/III:面向微控制器的RTOS

µC/OS-II/III是一款可移植、可伸缩、抢占式、实时且确定性的多任务内核。它使用高度可移植的ANSI C编写,仅少量代码使用汇编语言,以方便移植。其体积小巧,可伸缩至5至24K字节。

µC/OS-II到µC/OS-III的演变,反映了嵌入式系统日益增长的复杂性。µC/OS-II最多可管理64个任务,每个任务具有唯一的优先级。而µC/OS-III作为其增强版,最大的区别在于支持

无限数量的任务和优先级级别,其数量仅受处理器内存的限制。它还支持多个任务运行在同一优先级,并使用时间片轮转调度。此外,µC/OS-III的“近乎为零的中断禁用时间” 确保了对最快中断源的响应,这是其确定性优势的核心体现。µC/OS-II/III被广泛应用于航空电子、医疗设备、数据通信、工业控制、消费电子和汽车等多个嵌入式领域。

1.7.2.7 VxWorks:任务关键领域的王者

VxWorks是美国风河系统(Wind River)公司于1983年开发的专有嵌入式RTOS。它以高可靠性、高性能内核和友好开发环境而闻名。它是一款确定性、基于优先级的抢占式RTOS,具有低延迟和最小抖动,因此非常适合硬实时嵌入式应用。

VxWorks的内核被归类为微内核,这使其具有更好的模块化和可扩展性。由于其卓越的实时性能和可靠性,VxWorks在航空航天、军事和机器人等对实时性要求极高的领域占据主导地位 。其成功并非偶然,它证明了在某些极端重要、不容有失的应用场景中,技术上的绝对确定性和久经考验的可靠性是超越成本和开源灵活性的首要考量。其在火星探测任务中的应用就是一个最强有力的佐证:当一个系统部署在数亿公里之外时,其故障的代价是无法承受的。这使得VxWorks在这一特定市场形成了难以逾越的壁垒。

1.7.2.8 QNX:微内核与汽车电子的领导者

QNX是一款商业类Unix实时操作系统,核心是其微内核架构 。在这种架构中,操作系统中的大多数功能都是以小型“服务器”的形式运行的 。这种模块化设计使其更加灵活、可扩展,且比传统单内核更安全。 QNX OS 8.0维护并改进了硬实时功能,具有严格的时间限制和响应时间保证 。它完全是抢占式的,并具有超高的延迟和抖动性能,这对于任务关键型系统至关重要。 QNX在汽车市场的占有率已达到75% 。其在汽车电子领域的成功是其微内核架构优势的完美体现。在现代“软件定义汽车”(Software-Defined Vehicle)中,一个芯片可能同时运行信息娱乐、高级驾驶辅助系统(ADAS)和仪表盘显示等功能 。在这种复杂且安全敏感的环境下,微内核能够将各个功能模块隔离,防止一个模块的崩溃影响到其他关键模块,这从根本上解决了安全和功能隔离的挑战。这种根本性的架构优势解释了为何汽车制造商愿意为其高昂的授权付费。

1.7.2.9 鸿蒙(HarmonyOS):面向万物互联的分布式新范式

鸿蒙是华为推出的一款面向全场景的分布式操作系统。它整体采用分层设计,内核层采用多内核设计,支持不同资源受限的设备选用适合的OS内核,如Linux内核或自研的LiteOS-M微内核。 其核心技术特点包括:

- 分布式能力:核心在于“超级终端”的概念,允许不同设备(手机、平板、手表等)像一个单一的“超级设备”一样协同工作并共享资源。

- 一次开发、多端部署:开发者只需编写一次代码,即可在多种终端设备上部署应用,这极大地提高了开发效率。

- 原子化服务(Atomic Services):这是一种轻量化的程序实体,无需安装,可由系统框架后台安装后直接使用,从而实现服务更快触达用户。

- 确定时延引擎:通过确定时延引擎和高性能IPC(进程间通信),实现系统天生流畅,降低应用响应延迟。

鸿蒙系统代表了嵌入式操作系统的一个全新发展方向:从“单设备”到“多设备协同”。它试图解决物联网(IoT)设备生态碎片化的问题,通过一个统一的软件平台,实现设备之间的无缝连接和资源共享。这不仅仅是技术创新,更是一种商业模式和生态构建的创新。其“多内核”设计是一种巧妙的策略,旨在利用Linux的成熟生态和微内核的安全性,同时兼顾不同设备的资源需求。

1.7.3 综合比较:关键特性、市场定位与行业洞察

1.7.3.1 技术架构对比:单内核、混合内核与微内核

嵌入式操作系统的架构决定了其性能、可靠性和扩展性,主要可分为三类:

- 单内核(Monolithic):所有核心功能(进程管理、文件系统、驱动等)都在内核空间运行。

- 代表:嵌入式Linux、uClinux。

- 特点:优点是性能高,因为组件间通信开销小。缺点是模块间耦合度高,一个驱动的崩溃可能导致整个系统崩溃。

- 微内核(Microkernel):内核只包含最基本的功能(如线程调度、内存管理、IPC),其他服务(文件系统、驱动)作为独立进程在用户空间运行。

- 代表:QNX、VxWorks。

- 特点:优点是高可靠性、高安全性和模块化,易于调试和扩展。一个用户空间服务的崩溃不会影响内核或其他服务。缺点是性能开销高于单内核,因为需要更多的进程间通信。

- 混合内核/多内核(Hybrid/Multi-kernel):结合了单内核和微内核的优点,部分功能在内核中以提高性能,同时将一些服务移至用户空间以增强可靠性。

- 代表:Symbian、鸿蒙HarmonyOS。

- 特点:鸿蒙更是创新性地支持在不同设备上运行不同的内核,以适应硬件的多样性,这是一种巧妙的混合策略。

1.7.3.2 实时性能与可靠性深度评估

实时性并非一个单一指标,它涉及确定性、上下文切换效率、中断处理速度和内存管理等多个方面。虽然开源通用操作系统可以通过补丁增强实时性,但专有商业RTOS在设计之初就以满足严格的时序要求为核心,其架构本身就为可靠性和确定性提供了结构性保障。

下表对各操作系统的关键特性进行了综合对比。

嵌入式操作系统综合特性对比

| 操作系统名称 | 内核类型 | 源码模式 | 典型资源占用 | 关键特性 | 主要应用领域 |

|---|---|---|---|---|---|

| 嵌入式Linux | 单内核 | 开放源码 | 约2 MiB起 | 开放源码,成熟稳定,兼容性好 | 智能设备、网关、消费电子 |

| uClinux | 单内核 | 开放源码 | 极小(无MMU) | 无MMU,无法实现虚拟内存 | 资源受限的微控制器 |

| Windows CE | RTOS微内核/混合内核 | 专有 | 小型 | 组件化,原生代码访问,多点触控 | 零售、医疗、工业制造 |

| PalmOS | 专有 | 专有 | 小型 | 为PDA设计,事件驱动 | 个人数字助理(已衰落) |

| Symbian | RTOS微内核/混合内核 | 曾开源后专有 | 小型 | 事件驱动,省内存,长续航 | 智能手机(已停止发展) |

| eCos | RTOS微内核/混合内核 | 开放源码 | 10 KB起 | 高度可配置,模块化设计 | 小型系统、启动引导程序 |

| µC/OS-II/III | RTOS内核 | 专有 | 5-24 KB(可伸缩) | 抢占式,确定性,可扩展 | 医疗、汽车、航空电子、消费电子 |

| VxWorks | RTOS微内核 | 专有 | 高性能 | 确定性,高可靠性,多核支持 | 航空航天、军事、工业控制、机器人 |

| QNX | RTOS微内核 | 专有 | 高性能 | 模块化,硬实时,低延迟/抖动 | 汽车、工业、国防、医疗 |

| 鸿蒙 HarmonyOS | 多内核(微内核) | 开放源码 | 视设备而定 | 分布式能力,多端部署,原子化服务 | 全场景智能终端、IoT设备 |

实时操作系统(RTOS)性能与可靠性对比

| 操作系统名称 | 实时性分类 | 确定性 | 低延迟/抖动 | 高可靠性 | 任务管理 |

|---|---|---|---|---|---|

| 嵌入式Linux | 软/硬实时 | 通过补丁增强 | 依赖于补丁与配置 | 良好 | 丰富的任务调度策略 |

| uClinux | 软实时 | 一般 | 一般 | 一般 | 依赖于无MMU的进程管理 |

| Windows CE | 硬实时 | 良好 | 良好 | 良好 | 组件化,可自定义 |

| Symbian | 硬实时 | 良好 | 良好 | 良好 | 抢占式多任务,多线程 |

| eCos | 硬实时 | 良好 | 良好 | 良好 | 依赖于模块化配置 |

| µC/OS-II/III | 硬实时 | 优秀 | 优秀 | 优秀 | 优先级抢占,可扩展 |

| VxWorks | 硬实时 | 卓越 | 卓越 | 卓越 | 基于优先级的抢占式调度 |

| QNX | 硬实时 | 卓越 | 卓越 | 卓越 | 严格的时间限制与响应保证 |

| 鸿蒙 HarmonyOS | 硬实时 | 良好 | 良好 | 良好 | 确定时延引擎,高性能IPC |

1.7.3.3 市场格局与竞争态势

嵌入式操作系统市场高度碎片化,没有一个单一的赢家通吃。这种格局是由不同领域对成本、可靠性和功能的不同需求所决定的。

根据市场分析,实时操作系统(RTOS)在全球嵌入式软件市场中占据主导地位,在2024年以超过40.0%的收入份额领先。北美是最大的市场,亚太地区增长最快。汽车领域是最大的最终用户,这印证了汽车行业对实时性、安全性和软件复杂性的高要求。

在市场中,开源(嵌入式Linux、eCos)和商业(VxWorks、QNX)模式并存。开源模式以低成本和高灵活性吸引了大量开发者和消费电子市场,而商业模式则凭借其高可靠性、专业技术支持和长期认证在任务关键型领域建立了护城河。这种市场格局的形成是由“需求”决定的,对成本敏感的消费电子产品倾向于选择开源和低成本方案;而对安全和可靠性敏感的汽车、航空领域则更倾向于选择那些拥有多年成功案例、经过严格认证的商业化RTOS。这是一种基于风险和价值的理性选择。

1.7.4 趋势展望与未来挑战

嵌入式操作系统的未来发展将紧密结合以下几个核心技术趋势,以应对日益复杂的应用场景:

- 人工智能与边缘计算:AI和机器学习(ML)的集成使得嵌入式设备能够进行实时数据处理和决策,这在自动驾驶和工业自动化等领域至关重要。边缘计算则将计算能力从云端推向数据源头,减少对网络连接的依赖,降低延迟并保护隐私。

- 多核微控制器与容器化:随着多核处理器的普及,并行处理成为可能,简化了调试和软件开发。容器化技术则通过提供抽象环境,解决了传统嵌入式软件工具链不一致、单体软件难以调试的问题,提高了开发效率。

- 增强的安全与功能安全:随着物联网设备的激增,嵌入式系统的网络安全已成为首要关注点。功能安全标准(如ISO 26262)变得越来越重要,特别是在汽车等领域。系统需要能够即使在故障条件下也能保持可预测的行为并继续运行,以确保用户安全。

- “一次开发、多端部署”的新范式:以鸿蒙为代表的分布式操作系统,旨在通过统一的开发平台和分布式技术,解决不同设备之间互联互通的障碍,提供无缝、一致的用户体验 。这是一种从硬件适配到软件协同的范式转变,预示着未来的嵌入式系统将不再是孤立的设备,而是无缝协作的智能网络的一部分。

嵌入式操作系统的选择是一个复杂的决策过程,需要综合考量项目需求、成本预算、风险容忍度和开发周期。本报告的分析揭示,没有一个“万能”的操作系统,每个系统都在特定的细分市场中找到了自己的定位。

- 成本敏感型应用:对于消费电子、智能家居和普通物联网设备等对成本敏感、但对实时性要求不极致的应用,嵌入式Linux是理想选择。其开放源码、丰富的生态和低廉的开发成本使其具有无可比拟的优势。

- 资源极度受限型应用:对于那些缺乏MMU或资源极其有限的微控制器应用,uClinux和eCos是精简且可行的解决方案,可根据具体需求选择。

- 高可靠性与确定性型应用:对于航空航天、军事、医疗设备和工业控制等对安全和可靠性有极致要求的任务关键型应用,VxWorks和QNX是无可争议的首选。它们以其原生的硬实时性能、经过多年实践验证的稳定性和专业的商业支持,为这些高风险应用提供了结构性保障。

- 万物互联与多端协同型应用:对于旨在构建跨设备无缝体验的物联网生态系统,以鸿蒙为代表的分布式操作系统提供了全新的解决方案和技术架构。其一次开发、多端部署的理念和分布式能力为未来的智能互联世界奠定了基础。

展望未来,嵌入式操作系统市场将继续演进。技术融合、生态竞争和安全合规将成为主导力量。成功的产品将是那些能够利用人工智能和边缘计算提升设备智能、通过容器化和多核技术提高开发效率、并通过原生设计和严格标准确保安全和可靠性的系统。

1.8 嵌入式系统的四层结构

嵌入式系统的软件架构通常采用分层设计,分为驱动层、操作系统(OS)层、中间件层和应用程序层。这种结构通过模块化和抽象化,优化了软硬件交互,提高了系统的可移植性、可维护性和开发效率。飞腾派基于E2000D SoC,采用四层结构,支持嵌入式Linux、RTOS和AI应用,体现了国产化与高性能的结合。到2025年,随着边缘AI和物联网的普及,分层架构进一步集成AI中间件和5G协议栈,市场规模预计增长20%。 本小节结合IEEE对嵌入式系统软件设计的定义(模块化与抽象化)和国内“十四五”规划对自主可控技术的要求,详细阐述四层结构及其在飞腾派中的应用,通过图示和案例为学生提供清晰的学习框架。

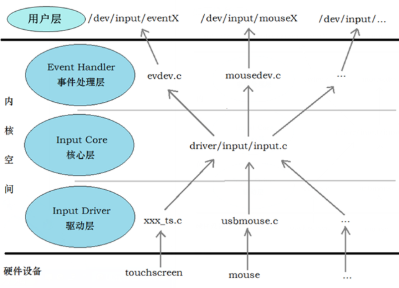

1.8.1 驱动层

驱动层是嵌入式系统与硬件交互的核心,为上层软件提供标准化的设备访问接口,确保应用程序无需关注硬件细节。驱动层程序是嵌入式系统中不可或缺的部分,任何外部设备(如GPIO、UART、I2C、传感器)都需要相应的驱动支持。驱动层通常包括以下组件:

- 硬件抽象层(HAL): 提供统一的硬件操作接口,屏蔽不同硬件平台的差异,提高系统可移植性。

- 板级支持包(BSP): 提供访问硬件设备寄存器的函数包,针对特定硬件平台(如飞腾派E2000D)定制,包含启动代码、时钟配置和外设初始化函数。

- 设备驱动程序: 直接管理特定外设(如温湿度传感器、显示屏),实现数据读写和控制逻辑。

功能与作用: 驱动层为上层软件提供标准接口(如Linux的/dev设备节点),隐藏硬件寄存器操作细节。例如,飞腾派上运行的I2C驱动允许应用程序通过ioctl()调用读取传感器数据,无需直接操作寄存器。

图 1.29 驱动层结构示意图

1.8.2 操作系统(OS)层

操作系统(OS)层负责管理和控制硬件资源(如内存、多任务、外设),为上层提供统一的运行环境和资源调度机制。嵌入式OS根据系统需求分为实时操作系统(RTOS) 和分时操作系统(如嵌入式Linux),飞腾派支持两者,适应多样化场景。

- 适用场景: OS层在以下情况下至关重要:

- 多任务复杂调度: 系统运行多个任务,需复杂任务调度和内存分配(如优先级抢占、虚拟内存)。

- 协议支持: 系统需集成网络协议(TCP/IP、MQTT)、文件系统(ext4)或数据库(SQLite)。

- 图形用户接口(GUI): 系统需支持Qt或Framebuffer,提供交互式界面。

- 核心功能: 隐藏硬件细节,提供抽象接口(如文件操作、线程管理),降低开发复杂度。飞腾派运行Armbian Linux,支持多任务调度,2025年优化AI任务优先级,提升推理效率20%。

- 典型OS:

- RTOS: μC/OS-III、VxWorks,微秒级响应,适合硬实时应用(如飞腾派工业控制)。

- 分时OS: 嵌入式Linux、鸿蒙,适合多媒体和物联网应用,飞腾派支持Linux 5.15内核,提供GUI和网络栈。

1.8.3 中间件层

中间件层位于OS和应用程序之间,提供通用服务和协议支持,简化复杂功能开发。在2025年,中间件技术在嵌入式系统中广泛应用,尤其在AI和物联网领域,飞腾派支持多种中间件,优化系统集成。

- 主要类型:

- 嵌入式Java: 提供跨平台运行环境,适合企业级物联网应用(如Java ME)。

- 嵌入式DCOM: 支持分布式组件对象模型,适用于工业自动化通信。

- 面向应用领域的中间件: 包括网络协议栈(MQTT、CoAP)、GUI库(Qt)、数据库(SQLite)。

- 功能与作用: 中间件封装通用功能(如网络通信、数据管理),降低应用程序开发难度。

1.8.4 应用程序层

应用程序层由多个相对独立的应用任务组成,完成嵌入式系统的特定功能,由OS调度运行。飞腾派支持多样化应用,2025年新增AI视觉和工业控制任务支持。

- 典型任务:

- I/O任务: 传感器数据采集、执行器控制,如飞腾派GPIO控制LED闪烁。

- 计算任务: 数据处理、AI推理,如飞腾派运行TensorFlow Lite模型进行图像分类。

- 通信任务: 数据传输、云端交互,如飞腾派通过MQTT上报环境数据。

- 功能与作用: 应用程序直接实现用户需求,依赖OS的任务调度和中间件的协议支持。

嵌入式系统的四层结构(驱动层、OS层、中间件层、应用程序层)通过模块化和抽象化,实现高效的软硬件协同。

1.9 飞腾派开发板核心特性

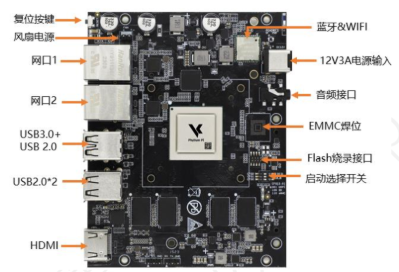

本小节将聚焦于本书的核心实践平台——飞腾派(Phytium Pi),介绍其作为国产嵌入式开发平台的核心技术价值、核心配置以及在当前市场中的定位。到2025年,飞腾派已演进为高性能边缘计算平台,兼容ARMv8架构,支持国产操作系统如统信UOS,并优化AI和物联网应用。根据Phytium官方数据,2025年生态合作伙伴超过7300家,推动国产化进程。 本小节遵循中外教材编写原则:结合IEEE对嵌入式平台的定义(强调集成性和可靠性),以及国内“十四五”规划对国产硬件的要求,理论与实践融合,提供规格细节、对比分析和应用示例,帮助学生从工程视角评估平台选择。

1.9.1 硬件架构与设计理念

飞腾派开发板是基于飞腾 E2000D 系列处理器(或其衍生型号)设计的一款高性能、低功耗、高度集成的国产嵌入式平台。它继承了飞腾处理器在服务器和桌面领域的技术积累,并针对边缘计算和嵌入式应用进行了优化。到2025年,飞腾派已支持Armbian Linux等发行版,SDK更新包括新板配置和驱动优化。 这使得它适合教育、原型开发和工业部署。

1. 核心硬件架构

飞腾派的硬件架构亮点在于其采用了异构多核架构和丰富的片上系统(SoC)集成,到2025年,优化了实时响应和AI加速:

- CPU 核心: 采用飞腾自主设计的 FTC 核心(兼容 ARMv8 指令集),通常以 高性能大核(如 FTC664)和低功耗小核(如 FTC310)的异构方式协同工作,实现能效比最大化。八核配置运行于2.3 GHz,针对桌面和嵌入式优化。

- 集成 GPU: 板载高性能 Mali 系列图形处理器,提供强大的 2D/3D 图形渲染能力,支持 4K 高分辨率输出,使其适用于多媒体、图形界面和简单视觉应用。2025年,支持OpenGL ES 3.2和Vulkan,提升游戏和AI渲染。

- 丰富接口集成: 芯片集成了内存控制器(支持 LPDDR4/DDR4)、高速 I/O 控制器(USB 3.0、PCIe)以及大量的嵌入式外设接口(UART、SPI、I2C、GPIO)。到2025年,新增GPIO触发测试,支持实时应用。

2. 设计理念:国产自主与生态开放

飞腾派的设计理念紧密围绕国家战略和嵌入式应用需求,到2025年,强调安全和绿色计算:

- 国产自主可控: 核心处理器(FTC 核心)拥有自主知识产权,确保了供应链的安全性和系统的可靠性。2025年,Phytium生态覆盖7300+伙伴,支持国产硬件软件。

- 安全可靠: 飞腾处理器集成了安全扩展和加密加速单元,支持可信计算和数据安全传输,是高安全等级应用的首选。到2025年,优化为确定性响应时间<0.5µs。

- 面向边缘 AI 与 IoT: 强大的 CPU 算力和集成的 GPU/NPU 潜力,使其成为边缘计算网关、AI 视觉终端的理想载体。2025年,支持AI模型部署。

- 模块化与可扩展性: 通过标准的 40 针 GPIO 接口和 PCIe 扩展,极大地方便了外设连接和功能扩展,适合教育和快速原型开发。兼容Raspberry Pi布局,便于迁移。

1.9.2 性能参数与核心配置

飞腾派作为一款高性能开发板,其配置参数在同类产品中极具竞争力:

表 1-3 飞腾派性能参数

| 关键配置项 | 典型参数 | 性能意义与优势 |

|---|---|---|

| 中央处理器(CPU) | 飞腾 E2000D 系列,最高频率可达 2.3 GHz,八核 FTC 核心。 | 提供强大的通用计算能力,满足嵌入式 Linux 下复杂应用和服务的需求,支持多任务和AI推理。 |

| 内存(RAM) | 4GB/8GB/16GB LPDDR4 或 DDR4。 | 高速、大容量内存,支持多任务、数据库和轻量级 AI 模型部署。到2025年,带宽优化20%。 |

| 存储器(Storage) | 32GB/64GB/512GB eMMC/NVMe 板载高速存储,支持 SD 卡扩展。 | 提供快速的系统启动和稳定的数据读写性能,eMMC 比 SD 卡更可靠,支持NVMe高速。 |

| 图形处理器(GPU) | 集成 Mali 系列 GPU。 | 支持 OpenGL ES 等标准,可进行硬件加速的图形界面渲染和视频编解码。2025年,支持RX550外部GPU。 |

| 高速接口 | 多个 USB 3.0/2.0 接口,PCIe 扩展接口。 | 满足高速外设连接需求,如连接高速硬盘、采集卡或 5G 模块。到2025年,支持更高带宽。 |

| 显示输出 | HDMI 接口,支持 4K (3840x2160) 高清视频输出。 | 适用于多媒体终端、数字标牌和带有复杂 GUI 的设备。 |

| 功耗 | 典型工作功耗在 5W - 10W 范围。 | 功耗控制良好,适合长时间运行和散热受限的环境。2025年,优化为确定性响应。 |

1.9.3 与其他主流开发板的对比

将飞腾派与市场上主流的 ARM 架构开发板进行对比,能更清晰地认识其独特的市场定位。到2025年,对比强调AI性能和国产安全,飞腾派在自主性上突出。

表 1-4 飞腾派与其他主流开发板对比

| 特性维度 | 飞腾派 (Phytium Pi) | 树莓派 4 (Raspberry Pi 4) | NVIDIA Jetson Nano |

|---|---|---|---|

| 处理器架构 | ARMv8 兼容(FTC 核心)。 | ARMv8 (Cortex-A72)。 | ARMv8 (Cortex-A57)。 |

| 核心优势 | 国产自主、安全可控、异构多核。 | 生态极度成熟、价格亲民。 | 强大的 **AI/并行计算(CUDA)**能力。 |

| 多核性能 | 高核数版本多核性能出色,内存带宽高。 | 良好的多核性能,但通常受限于散热。 | CPU 性能适中,主要依赖 GPU 弥补。 |

| 功耗与发热 | 功耗适中,能效比高。 | 功耗低,发热量小。 | 功耗较高,需要主动散热,但在 AI 场景下性能更高。 |

| 生态成熟度 | 生态快速发展中,重点适配国产 OS,开源社区活跃度有待提高。 | 全球最成熟的 ARM 嵌入式开源生态。 | AI/深度学习生态(TensorFlow/PyTorch)强大。 |

| 应用定位 | 国产化应用、高安全需求、边缘计算网关。 | 基础物联网、教育、家庭影院、轻量级服务器。 | 实时图像识别、机器视觉、AI 机器人。 |

结论: 飞腾派是面向国产化应用、要求一定安全性和良好通用计算性能的边缘计算和 IoT 网关的理想平台。

1.10 小结

本章作为嵌入式系统与飞腾派开发的入门,系统介绍了嵌入式系统的核心概念、ARM处理器架构、飞腾派开发板特性以及课程学习路径,为深入学习嵌入式开发奠定了坚实基础。